Page 112 -

P. 112

3.4 / BUS INTERCONNECTION 85

Over the years, a number of interconnection structures have been tried. By far

the most common is the bus and various multiple-bus structures. The remainder of

this chapter is devoted to an assessment of bus structures.

3.4 BUS INTERCONNECTION

A bus is a communication pathway connecting two or more devices. A key charac-

teristic of a bus is that it is a shared transmission medium. Multiple devices connect

to the bus, and a signal transmitted by any one device is available for reception by all

other devices attached to the bus. If two devices transmit during the same time pe-

riod, their signals will overlap and become garbled. Thus, only one device at a time

can successfully transmit.

Typically, a bus consists of multiple communication pathways, or lines. Each

line is capable of transmitting signals representing binary 1 and binary 0. Over time,

a sequence of binary digits can be transmitted across a single line. Taken together,

several lines of a bus can be used to transmit binary digits simultaneously (in paral-

lel). For example, an 8-bit unit of data can be transmitted over eight bus lines.

Computer systems contain a number of different buses that provide pathways

between components at various levels of the computer system hierarchy.A bus that

connects major computer components (processor, memory, I/O) is called a system

bus. The most common computer interconnection structures are based on the use of

one or more system buses.

Bus Structure

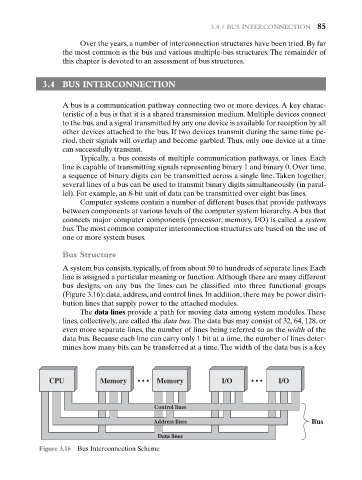

A system bus consists, typically, of from about 50 to hundreds of separate lines. Each

line is assigned a particular meaning or function.Although there are many different

bus designs, on any bus the lines can be classified into three functional groups

(Figure 3.16): data, address, and control lines. In addition, there may be power distri-

bution lines that supply power to the attached modules.

The data lines provide a path for moving data among system modules. These

lines, collectively, are called the data bus. The data bus may consist of 32, 64, 128, or

even more separate lines, the number of lines being referred to as the width of the

data bus. Because each line can carry only 1 bit at a time, the number of lines deter-

mines how many bits can be transferred at a time.The width of the data bus is a key

CPU Memory • • • Memory I/O • • • I/O

Control lines

Address lines Bus

Data lines

Figure 3.16 Bus Interconnection Scheme