Page 115 -

P. 115

88 CHAPTER 3 / A TOP-LEVEL VIEW OF COMPUTER FUNCTION

2. The bus may become a bottleneck as the aggregate data transfer demand

approaches the capacity of the bus. This problem can be countered to some

extent by increasing the data rate that the bus can carry and by using wider

buses (e.g., increasing the data bus from 32 to 64 bits). However, because the

data rates generated by attached devices (e.g., graphics and video controllers,

network interfaces) are growing rapidly, this is a race that a single bus is ulti-

mately destined to lose.

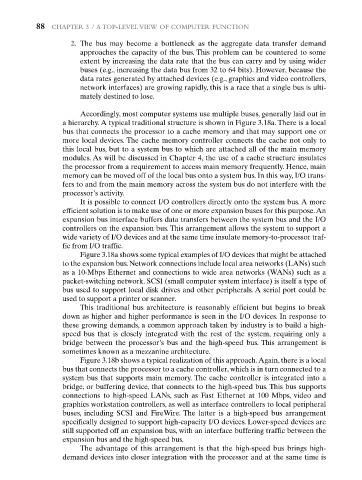

Accordingly, most computer systems use multiple buses, generally laid out in

a hierarchy.A typical traditional structure is shown in Figure 3.18a.There is a local

bus that connects the processor to a cache memory and that may support one or

more local devices. The cache memory controller connects the cache not only to

this local bus, but to a system bus to which are attached all of the main memory

modules. As will be discussed in Chapter 4, the use of a cache structure insulates

the processor from a requirement to access main memory frequently. Hence, main

memory can be moved off of the local bus onto a system bus. In this way, I/O trans-

fers to and from the main memory across the system bus do not interfere with the

processor’s activity.

It is possible to connect I/O controllers directly onto the system bus. A more

efficient solution is to make use of one or more expansion buses for this purpose.An

expansion bus interface buffers data transfers between the system bus and the I/O

controllers on the expansion bus. This arrangement allows the system to support a

wide variety of I/O devices and at the same time insulate memory-to-processor traf-

fic from I/O traffic.

Figure 3.18a shows some typical examples of I/O devices that might be attached

to the expansion bus. Network connections include local area networks (LANs) such

as a 10-Mbps Ethernet and connections to wide area networks (WANs) such as a

packet-switching network. SCSI (small computer system interface) is itself a type of

bus used to support local disk drives and other peripherals. A serial port could be

used to support a printer or scanner.

This traditional bus architecture is reasonably efficient but begins to break

down as higher and higher performance is seen in the I/O devices. In response to

these growing demands, a common approach taken by industry is to build a high-

speed bus that is closely integrated with the rest of the system, requiring only a

bridge between the processor’s bus and the high-speed bus. This arrangement is

sometimes known as a mezzanine architecture.

Figure 3.18b shows a typical realization of this approach.Again, there is a local

bus that connects the processor to a cache controller, which is in turn connected to a

system bus that supports main memory. The cache controller is integrated into a

bridge, or buffering device, that connects to the high-speed bus. This bus supports

connections to high-speed LANs, such as Fast Ethernet at 100 Mbps, video and

graphics workstation controllers, as well as interface controllers to local peripheral

buses, including SCSI and FireWire. The latter is a high-speed bus arrangement

specifically designed to support high-capacity I/O devices. Lower-speed devices are

still supported off an expansion bus, with an interface buffering traffic between the

expansion bus and the high-speed bus.

The advantage of this arrangement is that the high-speed bus brings high-

demand devices into closer integration with the processor and at the same time is