Page 120 -

P. 120

3.4 / BUS INTERCONNECTION 93

pausing for these signals to stabilize, it issues a read command, indicating the pres-

ence of valid address and control signals.The appropriate memory decodes the ad-

dress and responds by placing the data on the data line. Once the data lines have

stabilized, the memory module asserts the acknowledged line to signal the proces-

sor that the data are available. Once the master has read the data from the data

lines, it deasserts the read signal. This causes the memory module to drop the data

and acknowledge lines. Finally, once the acknowledge line is dropped, the master

removes the address information.

Figure 3.20b shows a simple asynchronous write operation. In this case, the

master places the data on the data line at the same time that is puts signals on the

status and address lines. The memory module responds to the write command by

copying the data from the data lines and then asserting the acknowledge line. The

master then drops the write signal and the memory module drops the acknowl-

edge signal.

Synchronous timing is simpler to implement and test. However, it is less flexi-

ble than asynchronous timing. Because all devices on a synchronous bus are tied to

a fixed clock rate, the system cannot take advantage of advances in device perfor-

mance. With asynchronous timing, a mixture of slow and fast devices, using older

and newer technology, can share a bus.

BUS WIDTH We have already addressed the concept of bus width. The width of the

data bus has an impact on system performance: The wider the data bus, the greater

the number of bits transferred at one time. The width of the address bus has an im-

pact on system capacity: the wider the address bus, the greater the range of locations

that can be referenced.

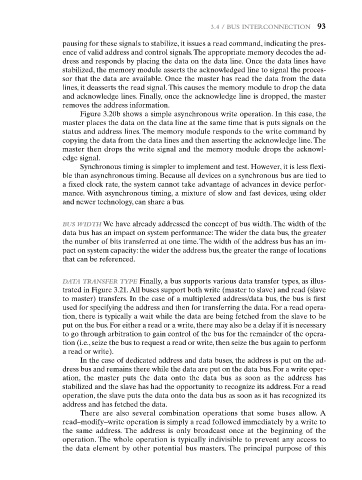

DATA TRANSFER TYPE Finally, a bus supports various data transfer types, as illus-

trated in Figure 3.21.All buses support both write (master to slave) and read (slave

to master) transfers. In the case of a multiplexed address/data bus, the bus is first

used for specifying the address and then for transferring the data. For a read opera-

tion, there is typically a wait while the data are being fetched from the slave to be

put on the bus. For either a read or a write, there may also be a delay if it is necessary

to go through arbitration to gain control of the bus for the remainder of the opera-

tion (i.e., seize the bus to request a read or write, then seize the bus again to perform

a read or write).

In the case of dedicated address and data buses, the address is put on the ad-

dress bus and remains there while the data are put on the data bus. For a write oper-

ation, the master puts the data onto the data bus as soon as the address has

stabilized and the slave has had the opportunity to recognize its address. For a read

operation, the slave puts the data onto the data bus as soon as it has recognized its

address and has fetched the data.

There are also several combination operations that some buses allow. A

read–modify–write operation is simply a read followed immediately by a write to

the same address. The address is only broadcast once at the beginning of the

operation. The whole operation is typically indivisible to prevent any access to

the data element by other potential bus masters. The principal purpose of this