Page 135 -

P. 135

106 CHAPTER 3 / A TOP-LEVEL VIEW OF COMPUTER FUNCTION

you make, and explain. Hint: Determine the number of bytes that can be transferred

per bus cycle.

3.6 Consider a computer system that contains an I/O module controlling a simple key-

board/printer teletype. The following registers are contained in the processor and

connected directly to the system bus:

INPR: Input Register, 8 bits

OUTR: Output Register, 8 bits

FGI: Input Flag, 1 bit

FGO: Output Flag, 1 bit

IEN: Interrupt Enable, 1 bit

Keystroke input from the teletype and printer output to the teletype are controlled

by the I/O module.The teletype is able to encode an alphanumeric symbol to an 8-bit

word and decode an 8-bit word into an alphanumeric symbol.

a. Describe how the processor, using the first four registers listed in this problem,

can achieve I/O with the teletype.

b. Describe how the function can be performed more efficiently by also employing IEN.

3.7 Consider two microprocessors having 8- and 16-bit-wide external data buses, re-

spectively. The two processors are identical otherwise and their bus cycles take just

as long.

a. Suppose all instructions and operands are two bytes long. By what factor do the

maximum data transfer rates differ?

b. Repeat assuming that half of the operands and instructions are one byte long.

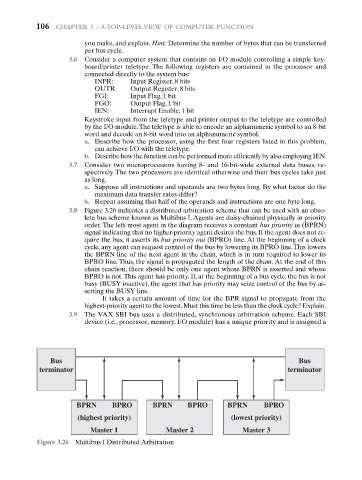

3.8 Figure 3.26 indicates a distributed arbitration scheme that can be used with an obso-

lete bus scheme known as Multibus I. Agents are daisy-chained physically in priority

order. The left-most agent in the diagram receives a constant bus priority in (BPRN)

signal indicating that no higher-priority agent desires the bus. If the agent does not re-

quire the bus, it asserts its bus priority out (BPRO) line. At the beginning of a clock

cycle, any agent can request control of the bus by lowering its BPRO line.This lowers

the BPRN line of the next agent in the chain, which is in turn required to lower its

BPRO line. Thus, the signal is propagated the length of the chain. At the end of this

chain reaction, there should be only one agent whose BPRN is asserted and whose

BPRO is not. This agent has priority. If, at the beginning of a bus cycle, the bus is not

busy (BUSY inactive), the agent that has priority may seize control of the bus by as-

serting the BUSY line.

It takes a certain amount of time for the BPR signal to propagate from the

highest-priority agent to the lowest.Must this time be less than the clock cycle? Explain.

3.9 The VAX SBI bus uses a distributed, synchronous arbitration scheme. Each SBI

device (i.e., processor, memory, I/O module) has a unique priority and is assigned a

Bus Bus

terminator terminator

BPRN BPRO BPRN BPRO BPRN BPRO

(highest priority) (lowest priority)

Master 1 Master 2 Master 3

Figure 3.26 Multibus I Distributed Arbitration