Page 130 -

P. 130

102 CHAPTER 3 / A TOP-LEVEL VIEW OF COMPUTER FUNCTION

g. During clock 6, the target places the third data item on the bus. However, in

this example, the initiator is not yet ready to read the data item (e.g., it has a

temporary buffer full condition). It therefore deasserts IRDY. This will cause

the target to maintain the third data item on the bus for an extra clock cycle.

h. The initiator knows that the third data transfer is the last, and so it deasserts

FRAME to signal the target that this is the last data transfer. It also asserts

IRDY to signal that it is ready to complete that transfer.

i. The initiator deasserts IRDY, returning the bus to the idle state, and the target

deasserts TRDY and DEVSEL.

Arbitration

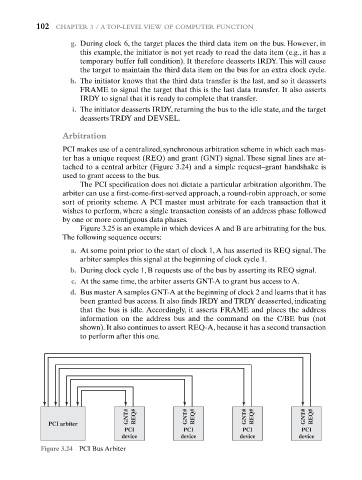

PCI makes use of a centralized, synchronous arbitration scheme in which each mas-

ter has a unique request (REQ) and grant (GNT) signal. These signal lines are at-

tached to a central arbiter (Figure 3.24) and a simple request–grant handshake is

used to grant access to the bus.

The PCI specification does not dictate a particular arbitration algorithm. The

arbiter can use a first-come-first-served approach, a round-robin approach, or some

sort of priority scheme. A PCI master must arbitrate for each transaction that it

wishes to perform, where a single transaction consists of an address phase followed

by one or more contiguous data phases.

Figure 3.25 is an example in which devices A and B are arbitrating for the bus.

The following sequence occurs:

a. At some point prior to the start of clock 1, A has asserted its REQ signal. The

arbiter samples this signal at the beginning of clock cycle 1.

b. During clock cycle 1, B requests use of the bus by asserting its REQ signal.

c. At the same time, the arbiter asserts GNT-A to grant bus access to A.

d. Bus master A samples GNT-A at the beginning of clock 2 and learns that it has

been granted bus access. It also finds IRDY and TRDY deasserted, indicating

that the bus is idle. Accordingly, it asserts FRAME and places the address

information on the address bus and the command on the C/BE bus (not

shown). It also continues to assert REQ-A, because it has a second transaction

to perform after this one.

GNT# REQ# GNT# REQ# GNT# REQ# GNT# REQ#

PCI arbiter

PCI PCI PCI PCI

device device device device

Figure 3.24 PCI Bus Arbiter