Page 161 -

P. 161

132 CHAPTER 4 / CACHE MEMORY

B 0 L 0

k lines

L k–1

Cache memory– set 0

B v–1

First v blocks of

main memory

(equal to number of sets)

Cache memory–set v–1

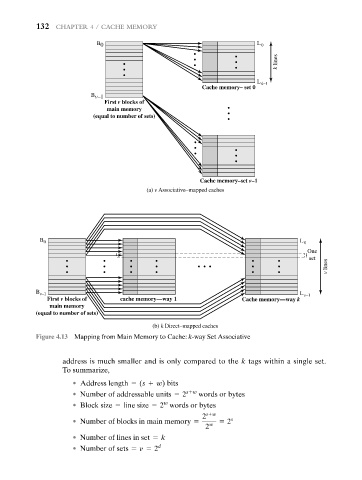

(a) v Associative–mapped caches

B 0 L 0

One

set

v lines

B v–1 L v–1

First v blocks of cache memory—way 1 Cache memory—way k

main memory

(equal to number of sets)

(b) k Direct–mapped caches

Figure 4.13 Mapping from Main Memory to Cache: k-way Set Associative

address is much smaller and is only compared to the k tags within a single set.

To summarize,

• Address length = (s + w) bits

• Number of addressable units = 2 s w words or bytes

• Block size = line size = 2 words or bytes

w

2 s+w

• Number of blocks in main memory = = 2 s

2 w

• Number of lines in set = k

• Number of sets = n = 2 d