Page 11 - DSP Integrated Circuits

P. 11

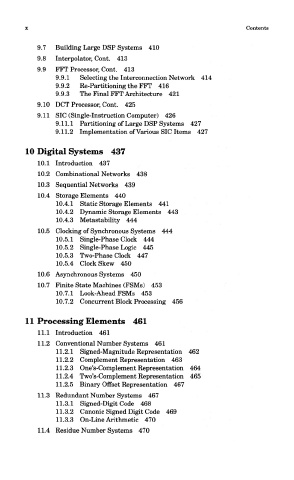

x Contents

9.7 Building Large DSP Systems 410

9.8 Interpolator, Cont. 413

9.9 FFT Processor, Cont. 413

9.9.1 Selecting the Interconnection Network 414

9.9.2 Re-Partitioning the FFT 416

9.9.3 The Final FFT Architecture 421

9.10 DCT Processor, Cont. 425

9.11 SIC (Single-Instruction Computer) 426

9.11.1 Partitioning of Large DSP Systems 427

9.11.2 Implementation of Various SIC Items 427

10 Digital Systems 437

10.1 Introduction 437

10.2 Combinational Networks 438

10.3 Sequential Networks 439

10.4 Storage Elements 440

10.4.1 Static Storage Elements 441

10.4.2 Dynamic Storage Elements 443

10.4.3 Metastability 444

10.5 Clocking of Synchronous Systems 444

10.5.1 Single-Phase Clock 444

10.5.2 Single-Phase Logic 445

10.5.3 Two-Phase Clock 447

10.5.4 Clock Skew 450

10.6 Asynchronous Systems 450

10.7 Finite State Machines (FSMs) 453

10.7.1 Look-Ahead FSMs 453

10.7.2 Concurrent Block Processing 456

11 Processing Elements 461

11.1 Introduction 461

11.2 Conventional Number Systems 461

11.2.1 Signed-Magnitude Representation 462

11.2.2 Complement Representation 463

11.2.3 One's-Complement Representation 464

11.2.4 Two's-Complement Representation 465

11.2.5 Binary Offset Representation 467

11.3 Redundant Number Systems 467

11.3.1 Signed-Digit Code 468

11.3.2 Canonic Signed Digit Code 469

11.3.3 On-Line Arithmetic 470

11.4 Residue Number Systems 470