Page 41 - DSP Integrated Circuits

P. 41

26 Chapter 1 DSP Integrated Circuits

the models belong to the same domain. The transformations needed to derive the

VLSI implementation are therefore not straightforward.

Experience gained from both software and hardware projects indicates that it

is important that all members of a design team share a common view of, not only

the design goals, but also of the design process [12]. Without such a common view

severe communication and coordination difficulties may arise in the design process.

1.7.1 System Design Methodology

Integrated circuit design, also called VLSI design, is the process of transforming

the structural description of the logic circuitry into a detailed physical layout. This

process is complex and error prone. It is therefore mandatory to adhere to a highly

structured design methodology for the integrated circuit design phase.

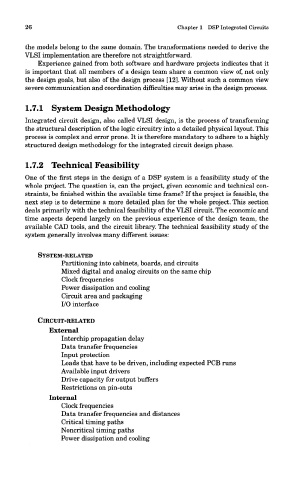

1.7.2 Technical Feasibility

One of the first steps in the design of a DSP system is a feasibility study of the

whole project. The question is, can the project, given economic and technical con-

straints, be finished within the available time frame? If the project is feasible, the

next step is to determine a more detailed plan for the whole project. This section

deals primarily with the technical feasibility of the VLSI circuit. The economic and

time aspects depend largely on the previous experience of the design team, the

available CAD tools, and the circuit library. The technical feasibility study of the

system generally involves many different issues:

SYSTEM-RELATED

Partitioning into cabinets, boards, and circuits

Mixed digital and analog circuits on the same chip

Clock frequencies

Power dissipation and cooling

Circuit area and packaging

I/O interface

CIRCUIT-RELATED

External

Interchip propagation delay

Data transfer frequencies

Input protection

Loads that have to be driven, including expected PCB runs

Available input drivers

Drive capacity for output buffers

Restrictions on pin-outs

Internal

Clock frequencies

Data transfer frequencies and distances

Critical timing paths

Noncritical timing paths

Power dissipation and cooling