Page 513 - DSP Integrated Circuits

P. 513

498 Chapter 11 Processing Elements

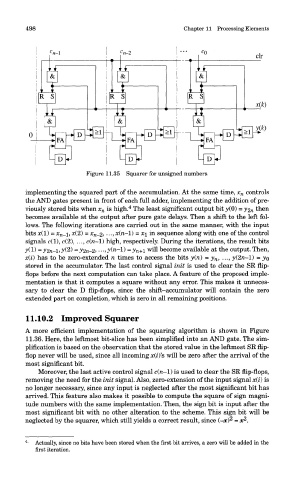

Figure 11.35 Squarer for unsigned numbers

implementing the squared part of the accumulation. At the same time, x n controls

the AND gates present in front of each full adder, implementing the addition of pre-

4

viously stored bits when x n is high. The least significant output bit y(0) = y% n then

becomes available at the output after pure gate delays. Then a shift to the left fol-

lows. The following iterations are carried out in the same manner, with the input

bits x(V) = x n_i, x(2) = x n_2, ••-, x(n-T> = xi in sequence along with one of the control

signals c(l), c(2), ..., c(rc-l) high, respectively. During the iterations, the result bits

yd) =y2n-l»y(2) =y2n-2, ...,y(n-l) = y n+i will become available at the output. Then,

xd) has to be zero-extended n times to access the bits y(n) = y n, ..., y(2n-l) = y$

stored in the accumulator. The last control signal init is used to clear the SR flip-

flops before the next computation can take place. A feature of the proposed imple-

mentation is that it computes a square without any error. This makes it unneces-

sary to clear the D flip-flops, since the shift-accumulator will contain the zero

extended part on completion, which is zero in all remaining positions.

11.10.2 Improved Squarer

A more efficient implementation of the squaring algorithm is shown in Figure

11.36. Here, the leftmost bit-slice has been simplified into an AND gate. The sim-

plification is based on the observation that the stored value in the leftmost SR flip-

flop never will be used, since all incoming x(i)'s will be zero after the arrival of the

most significant bit.

Moreover, the last active control signal c(n-T) is used to clear the SR flip-flops,

removing the need for the init signal. Also, zero-extension of the input signal x(i) is

no longer necessary, since any input is neglected after the most significant bit has

arrived. This feature also makes it possible to compute the square of sign magni-

tude numbers with the same implementation. Then, the sign bit is input after the

most significant bit with no other alteration to the scheme. This sign bit will be

2 2

neglected by the squarer, which still yields a correct result, since (-x) = x .

4

- Actually, since no bits have been stored when the first bit arrives, a zero will be added in the

first iteration.