Page 515 - DSP Integrated Circuits

P. 515

500 Chapter 11 Processing Elements

Here we can see that the result will contain an error in the accumulated sum.

But, since this error only exists in bits of higher significance than the result, this error

will not affect the output result. Further, if we sign extend the input signal with more

than 2/1-1 bits, the error will be scaled accordingly, and stay within the squarer. An

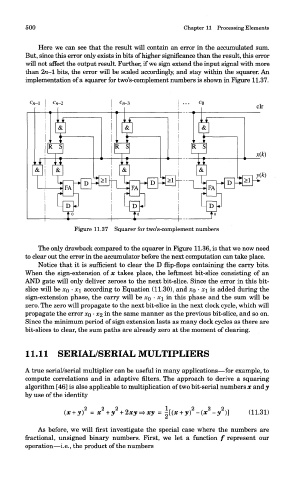

implementation of a squarer for two's-complement numbers is shown in Figure 11.37.

Figure 11.37 Squarer for two's-complement numbers

The only drawback compared to the squarer in Figure 11.36, is that we now need

to clear out the error in the accumulator before the next computation can take place.

Notice that it is sufficient to clear the D flip-flops containing the carry bits.

When the sign-extension of x takes place, the leftmost bit-slice consisting of an

AND gate will only deliver zeroes to the next bit-slice. Since the error in this bit-

slice will be XQ • xi according to Equation (11.30), and XQ • x\ is added during the

sign-extension phase, the carry will be XQ • x± in this phase and the sum will be

zero. The zero will propagate to the next bit-slice in the next clock cycle, which will

propagate the error XQ • X2 in the same manner as the previous bit-slice, and so on.

Since the minimum period of sign extension lasts as many clock cycles as there are

bit-slices to clear, the sum paths are already zero at the moment of clearing.

11.11 SERIAL/SERIAL MULTIPLIERS

A true serial/serial multiplier can be useful in many applications—for example, to

compute correlations and in adaptive filters. The approach to derive a squaring

algorithm [46] is also applicable to multiplication of two bit-serial numbers x and y

by use of the identity

As before, we will first investigate the special case where the numbers are

fractional, unsigned binary numbers. First, we let a function / represent our

operation—i.e., the product of the numbers