Page 516 - DSP Integrated Circuits

P. 516

11.11 Serial/Serial Multipliers 501

Then, the computation of f

can be carried out in n iterations

by repeatedly squaring the sum

of the most significant bit of a

number and the other bits of that

number. In the first step, f\ =

f(x) is decomposed into the

square of the most significant bit

of x with a rest term and a

remaining square /2-

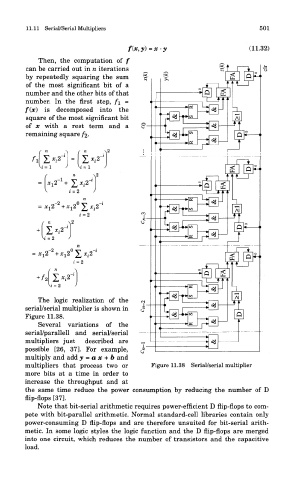

The logic realization of the

serial/serial multiplier is shown in

Figure 11.38.

Several variations of the

serial/parallell and serial/serial

multipliers just described are

possible [26, 37]. For example,

multiply and add y = a x + 6 and

multipliers that process two or Figure 11.38 Serial/serial multiplier

more bits at a time in order to

increase the throughput and at

the same time reduce the power consumption by reducing the number of D

flip-flops [37].

Note that bit-serial arithmetic requires power-efficient D flip-flops to com-

pete with bit-parallel arithmetic. Normal standard-cell libraries contain only

power-consuming D flip-flops and are therefore unsuited for bit-serial arith-

metic. In some logic styles the logic function and the D flip-flops are merged

into one circuit, which reduces the number of transistors and the capacitive

load.