Page 163 - Embedded Microprocessor Systems Real World Design

P. 163

1

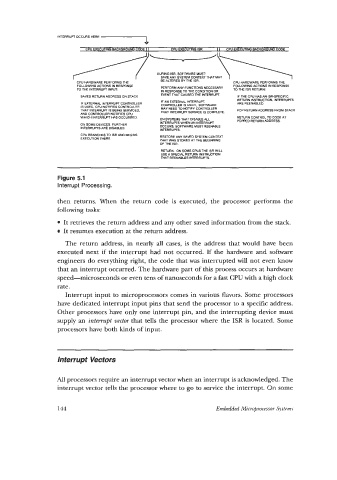

INTERRUPT OCCURS HERE

CPU EXECUTING EACKGROUNO CODE I I CPU WCMNG ISR I1 CPUU(ECMNGBAC K G R ~

DURING ISR. SOFTWARE MUST.

SAM ANY SYSTEM CONTEXT THAT MAY

CPU HARDWARE PERFORMS THE BE ALTERED BY THE ISR CPU HARDWARE PERFORMS THE

FOLLOWING ACTIONS IN RESPONSE FOLLOWING ACTIONS IN RESPONSE

TO THE INTERRUPT INPn PERFORM ANY FUNCTIONS NECESSARY TO THE ISR RETURN

IN RESPONSE TO THE CONDITION OR

SAVES RETURN ADDRESS ON STACK EVENT THAT CAUSED THE INTERRUPT IF THE CW HAS AN ISR-SPECIFIC

IF AN EXTERNAL INTERRUPT RETURN INSTRUCTION, INTERRVmS

F EXTERML IhTERRJPT CONTROLLER CONTROLLER IS USED, SOFTWARE ARE REENABLED.

45 USED CPJ NOTIFIES CONTROrLtH MAY NEED TO NOTIFY CONTROLLER

ThAT INTERRLPT S BEING SERWCED POP RETURN ADDRESS FROM STACK

AND CONTROLLER NOTIFIES CPL THAT IMERRUPT SERWCE IS COMPLETE

WHICH INTERRUPT HAS OCCURRED RETURN CONTROL TO CODE AT

ON SYSTEMS THAT DISABLE ALL POPPED RETURN ADDRESS

ON SOME DEVICES, FURTHER INTERRUPTS WHEN AN INTERRUPT

OCCURS, SOFTWARE MUST REENABLE

IUTERRUPTS ARE DISABLED

INTERRUPTS

CW BRANCHES TO ISR AND BEGINS RESTORE ANY SAVED SYSTEM CONTEXT

EXECUTION THERE.

THAT WAS STORED AT THE BEGINNING

OF THE ISR.

RETURN. ON SOME CPUS THE ISR WILL

USE A SPECIAL RETURN INSTRUCTION

THAT REENABLES INTERRUPTS

Figure 5.1

Interrupt Processing.

then returns. When the return code is executed, the processor performs the

following tasks:

It retrieves the return address and any other saved information from the stack.

It resumes execution at the return address.

The return address, in nearly all cases, is the address that would have been

executed next if the interrupt had not occurred. If the hardware and software

engineers do everything right, the code that was interrupted will not even know

that an interrupt occurred. The hardware part of this process occurs at hardware

speed-microseconds or even tens of nanoseconds for a fast CPU with a high clock

rate.

Interrupt input to microprocessors comes in various flavors. Some processors

have dedicated interrupt input pins that send the processor to a specific address.

Other processors have only one interrupt pin, and the interrupting device must

supply an interrupt vector that tells the processor where the ISR is located. Some

processors have both kinds of input.

Interrupt Vectors

All processors require an interrupt vector when an interrupt is acknowledged. The

interrupt vector tells the processor where to go to service the interrupt. On some

144 Embedded Microprocessor Svstpm r