Page 336 - Embedded Microprocessor Systems Real World Design

P. 336

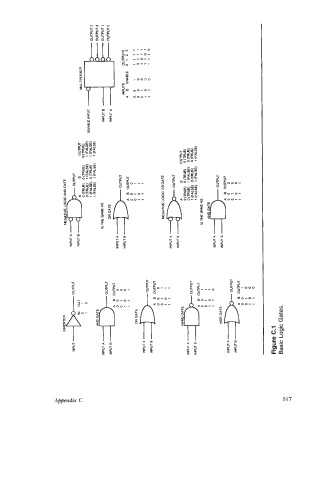

NEGATIM LOGIC AND GATE

INMRTER om:

INPUT A

INPUT OUTPUT

n INPUT B OWUE) O(TRUE) o (mw MULTIPLEXER

OUTPUT

1 0 0 (TRUE) 1 (FALSE) 1 (FALSE) ENABLE INPUT g--pZ;

1 (FALSE) o (TRUE) 1 (FALSE) OUTPUT 3

1 (FALSE) 1 (FALSE) 1 (FALSE)

33-

AND GATE

INPUT A IS THE SAME AS INPUT B

OUTPUT

INPUT B A B OUTPUT OR GATE INPUT A

00 0 INPUT A

0 1 0 INPUTS OUTPUTS

1 0 0 INPUT E A B ENABLE 0 1 2 3

11 1 A B OUTPUT

00 0 x x 1 1111

01

1

OR GATE

=E+ 1 1 0 1110

0

1011

INPUT A 1 11 1 1 0 0 1 0 1 0 0 0 0 0111

1101

OUTPUT

INPUTB A B OUTWT

00 0

0 1 1 NEGATIM LOGIC OR GATE

1 0 1

1 1 1 INPUT A

INWT E OUTPUT

=D- 1 (FALSE) 0 ClRUE) 0 (TRUE)

NAND GATE

0 (TRUE)

INPUT A 0 (TRUE) 1 (FALSE) 0 (TRUE)

OUTPUT

INPUT B A B OUTPUT 1 (FALSE) 1 (FALSE) 1 (FALSE)

00 1 IS THE SAME AS

0 1 1

1 0 1 AND GATE

1 1 0 INPUT A

OUTPUT

NOR GATE

0 0 01 0 0

INPUT A '-p OUTPUT

INPUT 8 1 0 0

A B OUTPUT 11 1

00 1

0 1 0

10 0

1 1 0

Figure C.l

Basic Logic Gates.