Page 328 - Hardware Implementation of Finite-Field Arithmetic

P. 328

308 Cha pte r T e n

next_a = b + a_div_2 + carry, carry

xx yy next_b = –(a_div_2 + carry)

P P

next_a next_b

yy

P

xx + yy

P P

ce_ab

x Q y Q initially: k initially: 0 load

xx P 01 sel_1 a b

y 1

(a =0)

start_addition (b =0)

point addition flag generation a 0

addition_done a x or b 0

1

xx P x 3 xx + yy P yy P y 3

P

1, 2 0 2 1 0

sel_2 squaring squaring

next_x Q next_y Q 0

initially: ce_Q ce_P

initially: x initially: y

1 load P P load

xx P yy P

x Q y Q Q_infinity

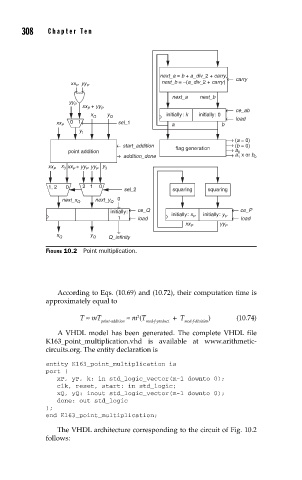

FIGURE 10.2 Point multiplication.

According to Eqs. (10.69) and (10.72), their computation time is

approximately equal to

2

T ≈ mT ≈ m (T + T ) (10.74)

point-addition mod-f-product mod-f-division

A VHDL model has been generated. The complete VHDL file

K163_point_multiplication.vhd is available at www.arithmetic-

circuits.org. The entity declaration is

entity K163_point_multiplication is

port (

xP, yP, k: in std_logic_vector(m-1 downto 0);

clk, reset, start: in std_logic;

xQ, yQ: inout std_logic_vector(m-1 downto 0);

done: out std_logic

);

end K163_point_multiplication;

The VHDL architecture corresponding to the circuit of Fig. 10.2

follows: