Page 81 - Hardware Implementation of Finite-Field Arithmetic

P. 81

64 Cha pte r T h ree

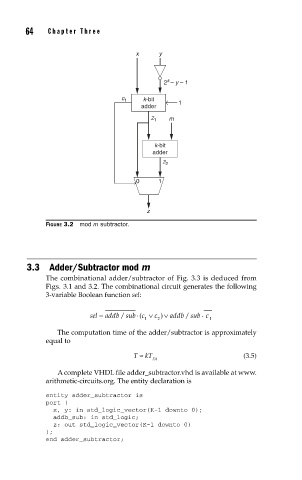

x y

k

2 – y – 1

c 1 k-bit

adder 1

z 1 m

k-bit

adder

z 2

0 1

z

FIGURE 3.2 mod m subtractor.

3.3 Adder/Subtractor mod m

The combinational adder/subtractor of Fig. 3.3 is deduced from

Figs. 3.1 and 3.2. The combinational circuit generates the following

3-variable Boolean function sel:

⋅

sel = addb sub c ∨ c ∨ addb sub c .

/

)

(

/

1 2 1

The computation time of the adder/subtractor is approximately

equal to

T ≈ kT (3.5)

FA

A complete VHDL file adder_subtractor.vhd is available at www.

arithmetic-circuits.org. The entity declaration is

entity adder_subtractor is

port (

x, y: in std_logic_vector(K-1 downto 0);

addb_sub: in std_logic;

z: out std_logic_vector(K-1 downto 0)

);

end adder_subtractor;