Page 86 - Hardware Implementation of Finite-Field Arithmetic

P. 86

mod m Operations 69

x y start

sequential carry-save

multiplier

done 1

to control unit

p p p

s c

start 2

from control unit

SRT reducer

z

done

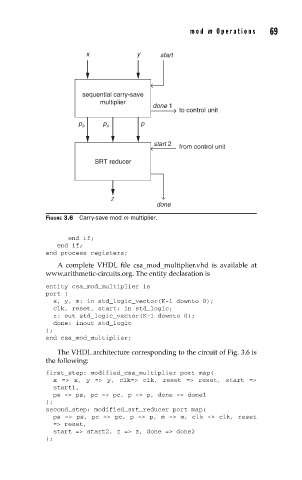

FIGURE 3.6 Carry-save mod m multiplier.

end if;

end if;

end process registers;

A com plete VHDL file csa_mod_multiplier.vhd is available at

www.arithmetic-circuits.org. The entity declaration is

entity csa_mod_multiplier is

port (

x, y, m: in std_logic_vector(K-1 downto 0);

clk, reset, start: in std_logic;

z: out std_logic_vector(K-1 downto 0);

done: inout std_logic

);

end csa_mod_multiplier;

The VHDL architecture corresponding to the circuit of Fig. 3.6 is

the following:

first_step: modified_csa_multiplier port map(

x => x, y => y, clk=> clk, reset => reset, start =>

start1,

ps => ps, pc => pc, p => p, done => done1

);

second_step: modified_srt_reducer port map(

ps => ps, pc => pc, p => p, m => m, clk => clk, reset

=> reset,

start => start2, z => z, done => done2

);