Page 82 - Hardware Implementation of Finite-Field Arithmetic

P. 82

mod m Operations 65

x y

addb/sub

c 1 k-bit

adder

z 1

m

c 2 k-bit

adder

comb.

circ. z 2

sel 0 1

z

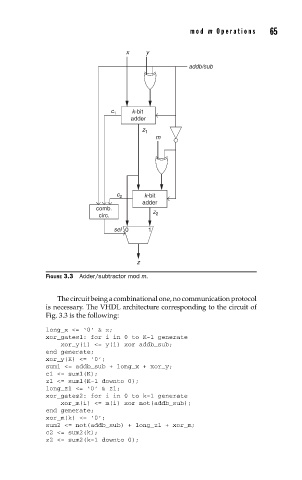

FIGURE 3.3 Adder/subtractor mod m.

The circuit being a combinational one, no communication protocol

is necessary. The VHDL architecture corresponding to the circuit of

Fig. 3.3 is the following:

long_x <= ‘0’ & x;

xor_gates1: for i in 0 to K-1 generate

xor_y(i) <= y(i) xor addb_sub;

end generate;

xor_y(K) <= ‘0’;

sum1 <= addb_sub + long_x + xor_y;

c1 <= sum1(K);

z1 <= sum1(K-1 downto 0);

long_z1 <= ‘0’ & z1;

xor_gates2: for i in 0 to k-1 generate

xor_m(i) <= m(i) xor not(addb_sub);

end generate;

xor_m(k) <= ‘0’;

sum2 <= not(addb_sub) + long_z1 + xor_m;

c2 <= sum2(k);

z2 <= sum2(k-1 downto 0);