Page 84 - Hardware Implementation of Finite-Field Arithmetic

P. 84

mod m Operations 67

x y

parallel

8-by-8

multiplier

product (15..0)

mod 239

reducer

z

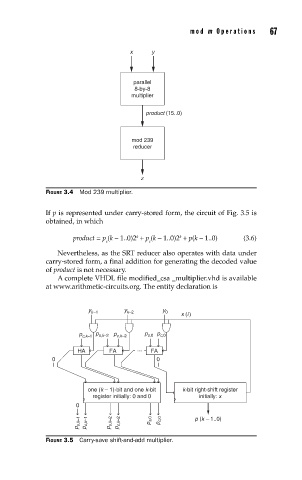

FIGURE 3.4 Mod 239 multiplier.

If p is represented under carry-stored form, the circuit of Fig. 3.5 is

obtained, in which

k

product = p (k − 1..0)2 + p (k − 1..0)2 + p(k − 1..0) (3.6)

k

s c

Nevertheless, as the SRT reducer also operates with data under

carry-stored form, a final addition for generating the decoded value

of product is not necessary.

A co mplete VHDL file modified_csa _multiplier.vhd is available

at www.arithmetic-circuits.org. The entity declaration is

y k–1 y k–2 y 0

x (i)

p c,k–1 p s,k–2 p c,k–2 p s,0 p c,0

HA FA ... FA

0 0

one (k – 1)-bit and one k-bit k-bit right-shift register

register initially: 0 and 0 initially: x

0

p s,k–1 p c,k–1 p s,k–2 p c,k–2 p s,0 p c,0 p (k – 1..0)

FIGURE 3.5 Carry-save shift-and-add multiplier.