Page 84 - Introduction to Microcontrollers Architecture, Programming, and Interfacing of The Motorola 68HC12

P. 84

3.2 Post Byte Index Addressing Modes 6!

address. These registers are called pointer or index registers. Obtaining an address from

such an index register would be faster because the number of bits needed to specify one of

a few registers is much less than the number of bits needed to specify any word in

memory that holds the address. Moreover, index addressing is the most efficient mode to

handle many data structures, such as character strings, vectors, and many others, as we

discuss later. With this potential, index registers have been used in a number of similar

modes, called collectively index addressing modes, which are introduced below.

Before we get into the modes of index addressing we have to discuss the idea of a

post byte. As noted earlier, the 6812 is a successor of the 6811. The latter had only the

modes inherent, immediate, page zero, direct, and one form of index addressing discussed

below. To keep the same customers that they had for the 6811 happy with the newer

machine. Motorola opted to make the 6812 as similar as possible to its predecessors. But

to introduce more addressing modes, they needed more room in the instruction. The 6812

is as similar to its predecessors as possible, using the same opcodes in many cases. The

extra addressing modes were provided by including an extra byte, right after the opcode

byte, for addressing information only and then only for variations of index addressing that

are used on the 6812. This byte is the post byte.

The 6812 uses index addressing with two index registers, X and Y, the stack pointer

SP and program counter PC. Although these have equivalent addressing capabilities, the

SP register and program counter have special uses that are discussed in later sections of

this chapter. Generally, all the addressing modes described for X below also apply to the

other registers. First, there are load instructions that can load these registers. For

example, the instruction

LDX #$843

will load the 16-bit X register with $843. It is machine coded very much like the LDAA

immediate instruction. (See the CPU12RG/D manual.) In the following examples,

assume X is $843.

The other registers can be loaded using similar instructions, and other addressing

modes can be used to get the two bytes to be put in the index register. In all cases, the

effective address determined by the instruction is used to get the first byte to be put into

the high byte of the index register. The effective address plus one is used to get the

second byte to be put into the low byte of the index register.

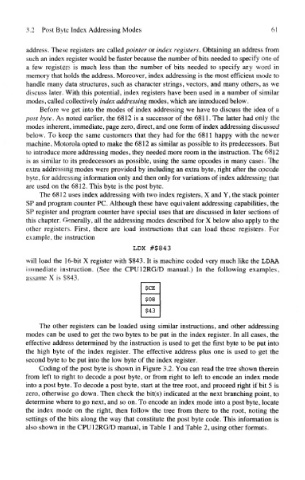

Coding of the post byte is shown in Figure 3.2. You can read the tree shown therein

from left to right to decode a post byte, or from right to left to encode an index mode

into a post byte. To decode a post byte, start at the tree root, and proceed right if bit 5 is

zero, otherwise go down. Then check the bit(s) indicated at the next branching point, to

determine where to go next, and so on. To encode an index mode into a post byte, locate

the index mode on the right, then follow the tree from there to the root, noting the

settings of the bits along the way that constitute the post byte code. This information is

also shown in the CPU12RG/D manual, in Table 1 and Table 2, using other formats.