Page 96 - Mechatronic Systems Modelling and Simulation with HDLs

P. 96

5.3 CO-SIMULATION BY SOFTWARE INTERPRETATION 85

main(argc,argv)

int argc;

char argv[]; Mem PIO

{

int i, j, stat;

double v1, v2;

...

while (true) {

v1 = mem[pio];

if (v1 > THRESH) {

if (!check(v1))

continue;

stat = getstat();

if (stat == 0) CPU

putstat(HARD);

...

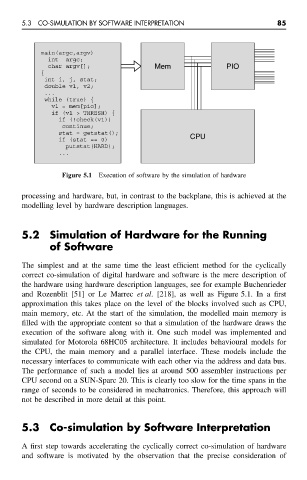

Figure 5.1 Execution of software by the simulation of hardware

processing and hardware, but, in contrast to the backplane, this is achieved at the

modelling level by hardware description languages.

5.2 Simulation of Hardware for the Running

of Software

The simplest and at the same time the least efficient method for the cyclically

correct co-simulation of digital hardware and software is the mere description of

the hardware using hardware description languages, see for example Buchenrieder

and Rozenblit [51] or Le Marrec et al. [218], as well as Figure 5.1. In a first

approximation this takes place on the level of the blocks involved such as CPU,

main memory, etc. At the start of the simulation, the modelled main memory is

filled with the appropriate content so that a simulation of the hardware draws the

execution of the software along with it. One such model was implemented and

simulated for Motorola 68HC05 architecture. It includes behavioural models for

the CPU, the main memory and a parallel interface. These models include the

necessary interfaces to communicate with each other via the address and data bus.

The performance of such a model lies at around 500 assembler instructions per

CPU second on a SUN-Sparc 20. This is clearly too slow for the time spans in the

range of seconds to be considered in mechatronics. Therefore, this approach will

not be described in more detail at this point.

5.3 Co-simulation by Software Interpretation

A first step towards accelerating the cyclically correct co-simulation of hardware

and software is motivated by the observation that the precise consideration of