Page 21 - Six Sigma for electronics design and manufacturing

P. 21

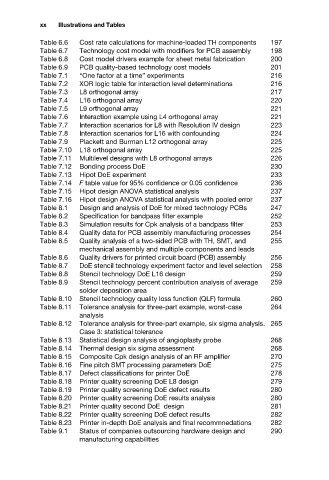

Illustrations and Tables

xx

Table 6.6

Technology cost model with modifiers for PCB assembly

198

Table 6.7

200

Cost model drivers example for sheet metal fabrication

Table 6.8

201

Table 6.9

PCB quality-based technology cost models

216

“One factor at a time” experiments

Table 7.1

Table 7.2

XOR logic table for interaction level determinations

216

217

Table 7.3

L8 orthogonal array

Table 7.4

L16 orthogonal array

220

L9 orthogonal array

221

Table 7.5

Interaction example using L4 orthogonal array

Table 7.6

221

223

Table 7.7 Cost rate calculations for machine-loaded TH components 197

Interaction scenarios for L8 with Resolution IV design

Table 7.8 Interaction scenarios for L16 with confounding 224

Table 7.9 Plackett and Burman L12 orthogonal array 225

Table 7.10 L18 orthogonal array 225

Table 7.11 Multilevel designs with L8 orthogonal arrays 226

Table 7.12 Bonding process DoE 230

Table 7.13 Hipot DoE experiment 233

Table 7.14 F table value for 95% confidence or 0.05 confidence 236

Table 7.15 Hipot design ANOVA statistical analysis 237

Table 7.16 Hipot design ANOVA statistical analysis with pooled error 237

Table 8.1 Design and analysis of DoE for mixed technology PCBs 247

Table 8.2 Specification for bandpass filter example 252

Table 8.3 Simulation results for Cpk analysis of a bandpass filter 253

Table 8.4 Quality data for PCB assembly manufacturing processes 254

Table 8.5 Quality analysis of a two-sided PCB with TH, SMT, and 255

mechanical assembly and multiple components and leads

Table 8.6 Quality drivers for printed circuit board (PCB) assembly 256

Table 8.7 DoE stencil technology experiment factor and level selection 258

Table 8.8 Stencil technology DoE L16 design 259

Table 8.9 Stencil technology percent contribution analysis of average 259

solder deposition area

Table 8.10 Stencil technology quality loss function (QLF) formula 260

Table 8.11 Tolerance analysis for three-part example, worst-case 264

analysis

Table 8.12 Tolerance analysis for three-part example, six sigma analysis. 265

Case 3: statistical tolerance

Table 8.13 Statistical design analysis of angioplasty probe 268

Table 8.14 Thermal design six sigma assessment 268

Table 8.15 Composite Cpk design analysis of an RF amplifier 270

Table 8.16 Fine pitch SMT processing parameters DoE 275

Table 8.17 Defect classifications for printer DoE 278

Table 8.18 Printer quality screening DoE L8 design 279

Table 8.19 Printer quality screening DoE defect results 280

Table 8.20 Printer quality screening DoE results analysis 280

Table 8.21 Printer quality second DoE design 281

Table 8.22 Printer quality screening DoE defect results 282

Table 8.23 Printer in-depth DoE analysis and final recommnedations 282

Table 9.1 Status of companies outsourcing hardware design and 290

manufacturing capabilities