Page 1132 - The Mechatronics Handbook

P. 1132

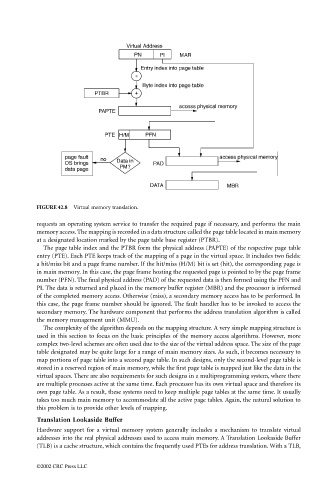

FIGURE 42.8 Virtual memory translation.

requests an operating system service to transfer the required page if necessary, and performs the main

memory access. The mapping is recorded in a data structure called the page table located in main memory

at a designated location marked by the page table base register (PTBR).

The page table index and the PTBR form the physical address (PAPTE) of the respective page table

entry (PTE). Each PTE keeps track of the mapping of a page in the virtual space. It includes two fields:

a hit/miss bit and a page frame number. If the hit/miss (H/M) bit is set (hit), the corresponding page is

in main memory. In this case, the page frame hosting the requested page is pointed to by the page frame

number (PFN). The final physical address (PAD) of the requested data is then formed using the PFN and

PI. The data is returned and placed in the memory buffer register (MBR) and the processor is informed

of the completed memory access. Otherwise (miss), a secondary memory access has to be performed. In

this case, the page frame number should be ignored. The fault handler has to be invoked to access the

secondary memory. The hardware component that performs the address translation algorithm is called

the memory management unit (MMU).

The complexity of the algorithm depends on the mapping structure. A very simple mapping structure is

used in this section to focus on the basic principles of the memory access algorithms. However, more

complex two-level schemes are often used due to the size of the virtual address space. The size of the page

table designated may be quite large for a range of main memory sizes. As such, it becomes necessary to

map portions of page table into a second page table. In such designs, only the second-level page table is

stored in a reserved region of main memory, while the first page table is mapped just like the data in the

virtual spaces. There are also requirements for such designs in a multiprogramming system, where there

are multiple processes active at the same time. Each processor has its own virtual space and therefore its

own page table. As a result, these systems need to keep multiple page tables at the same time. It usually

takes too much main memory to accommodate all the active page tables. Again, the natural solution to

this problem is to provide other levels of mapping.

Translation Lookaside Buffer

Hardware support for a virtual memory system generally includes a mechanism to translate virtual

addresses into the real physical addresses used to access main memory. A Translation Lookaside Buffer

(TLB) is a cache structure, which contains the frequently used PTEs for address translation. With a TLB,

©2002 CRC Press LLC