Page 314 - ARM 64 Bit Assembly Language

P. 314

Floating point 303

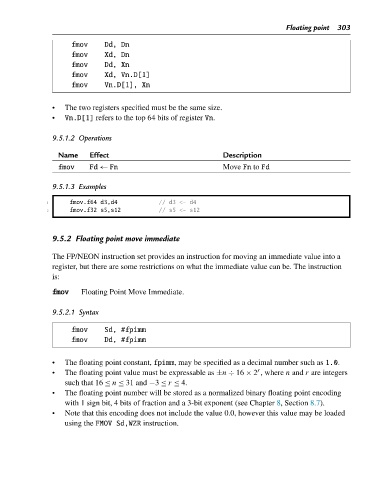

fmov Dd, Dn

fmov Xd, Dn

fmov Dd, Xn

fmov Xd, Vn.D[1]

fmov Vn.D[1], Xn

• The two registers specified must be the same size.

• Vn.D[1] refers to the top 64 bits of register Vn.

9.5.1.2 Operations

Name Effect Description

fmov Fd ← Fn Move Fn to Fd

9.5.1.3 Examples

1 fmov.f64 d3,d4 // d3 <- d4

2 fmov.f32 s5,s12 // s5 <- s12

9.5.2 Floating point move immediate

The FP/NEON instruction set provides an instruction for moving an immediate value into a

register, but there are some restrictions on what the immediate value can be. The instruction

is:

fmov Floating Point Move Immediate.

9.5.2.1 Syntax

fmov Sd, #fpimm

fmov Dd, #fpimm

• The floating point constant, fpimm, may be specified as a decimal number such as 1.0.

r

• The floating point value must be expressable as ±n ÷ 16 × 2 ,where n and r are integers

such that 16 ≤ n ≤ 31 and −3 ≤ r ≤ 4.

• The floating point number will be stored as a normalized binary floating point encoding

with 1 sign bit, 4 bits of fraction and a 3-bit exponent (see Chapter 8, Section 8.7).

• Note that this encoding does not include the value 0.0, however this value may be loaded

using the FMOV Sd,WZR instruction.