Page 309 - ARM 64 Bit Assembly Language

P. 309

298 Chapter 9

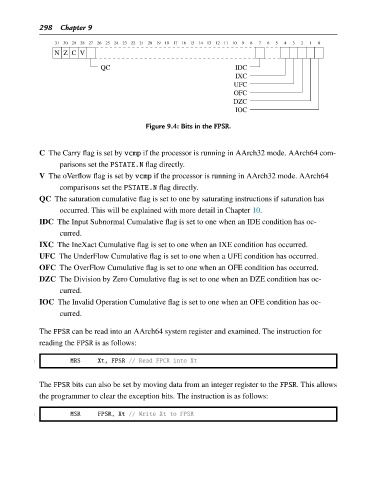

Figure 9.4: Bits in the FPSR.

C The Carry flag is set by vcmp if the processor is running in AArch32 mode. AArch64 com-

parisons set the PSTATE.N flag directly.

V The oVerflow flag is set by vcmp if the processor is running in AArch32 mode. AArch64

comparisons set the PSTATE.N flag directly.

QC The saturation cumulative flag is set to one by saturating instructions if saturation has

occurred. This will be explained with more detail in Chapter 10.

IDC The Input Subnormal Cumulative flag is set to one when an IDE condition has oc-

curred.

IXC The IneXact Cumulative flag is set to one when an IXE condition has occurred.

UFC The UnderFlow Cumulative flag is set to one when a UFE condition has occurred.

OFC The OverFlow Cumulative flag is set to one when an OFE condition has occurred.

DZC The Division by Zero Cumulative flag is set to one when an DZE condition has oc-

curred.

IOC The Invalid Operation Cumulative flag is set to one when an OFE condition has oc-

curred.

The FPSR can be read into an AArch64 system register and examined. The instruction for

reading the FPSR is as follows:

1 MRS Xt, FPSR // Read FPCR into Xt

The FPSR bits can also be set by moving data from an integer register to the FPSR. This allows

the programmer to clear the exception bits. The instruction is as follows:

1 MSR FPSR, Xt // Write Xt to FPSR