Page 308 - ARM 64 Bit Assembly Language

P. 308

Floating point 297

AHP Alternate Half Precision control bit.

0: Use IEEE half precision format

1: Use alternative half precision format.

DN Default NaN enable:

0: Disable Default NaN mode. NaN operands propagate through to the output of a

floating-point operation.

1: Enable Default NaN mode. Any operation involving one or more NaNs returns the

default NaN.

FZ Flush-to-Zero enable:

0: Disable Flush-to-Zero mode.

1: Enable Flush-to-Zero mode.

Flush-to-Zero mode replaces subnormal numbers with 0. This does not comply with IEEE

754 standard, but may increase performance.

RMODE Rounding mode:

00 Round to Nearest (RN).

01 Round towards Plus infinity (RP).

10 Round towards Minus infinity (RM).

11 Round towards Zero (RZ).

FZ16 Flush-to-zero mode control bit for half precision data processing instructions.

0: Disable Flush-to-Zero mode for half precision.

1: Enable Flush-to-Zero mode for half precision.

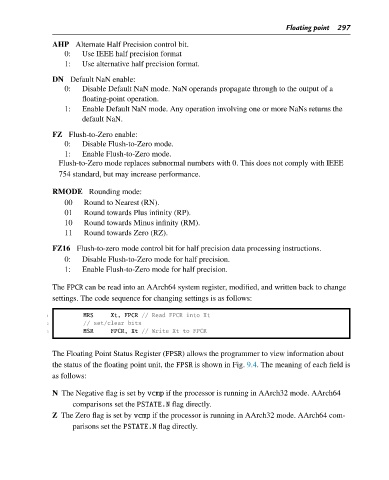

The FPCR can be read into an AArch64 system register, modified, and written back to change

settings. The code sequence for changing settings is as follows:

1 MRS Xt, FPCR // Read FPCR into Xt

2 // set/clear bits

3 MSR FPCR, Xt // Write Xt to FPCR

The Floating Point Status Register (FPSR) allows the programmer to view information about

the status of the floating point unit, the FPSR is showninFig. 9.4. The meaning of each field is

as follows:

N The Negative flag is set by vcmp if the processor is running in AArch32 mode. AArch64

comparisons set the PSTATE.N flag directly.

Z The Zero flag is set by vcmp if the processor is running in AArch32 mode. AArch64 com-

parisons set the PSTATE.N flag directly.