Page 312 - ARM 64 Bit Assembly Language

P. 312

Floating point 301

4 stur s0,[x1,#4]! // Add 4 to x1, then load s0 from

5 // the resulting address

9.4.3 Load/store pair

These instructions are used to load or store two registers at a time. This can be useful for mov-

ing registers onto the stack or for copying data. These two instructions are particularly useful

for transferring data in a load-store architecture because each instruction can move twice as

much information as the ldr and str instructions.

ldp Load Pair, and

stp Store Pair.

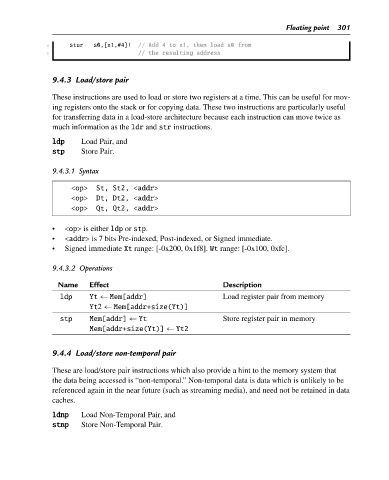

9.4.3.1 Syntax

<op> St, St2, <addr>

<op> Dt, Dt2, <addr>

<op> Qt, Qt2, <addr>

• <op> is either ldp or stp.

• <addr> is 7 bits Pre-indexed, Post-indexed, or Signed immediate.

• Signed immediate Xt range: [-0x200, 0x1f8]. Wt range: [-0x100, 0xfc].

9.4.3.2 Operations

Name Effect Description

ldp Yt ← Mem[addr] Load register pair from memory

Yt2 ← Mem[addr+size(Yt)]

stp Mem[addr] ← Yt Store register pair in memory

Mem[addr+size(Yt)] ← Yt2

9.4.4 Load/store non-temporal pair

These are load/store pair instructions which also provide a hint to the memory system that

the data being accessed is “non-temporal.” Non-temporal data is data which is unlikely to be

referenced again in the near future (such as streaming media), and need not be retained in data

caches.

ldnp Load Non-Temporal Pair, and

stnp Store Non-Temporal Pair.