Page 381 - Analog and Digital Filter Design

P. 381

378 Analog and Digital Filter Design

OUTPUT

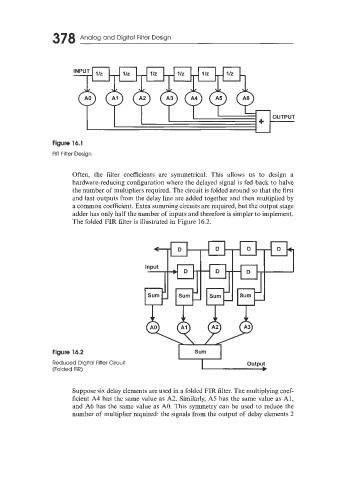

Figure 16.1

FIR Filter Design

Often, the filter coefficients are symmetrical. This allows us to design a

hardware-reducing configuration where the delayed signal is fed back to halve

the number of multipliers required. The circuit is folded around so that the first

and last outputs from the delay line are added together and then multiplied by

a common coefficient. Extra summing circuits are required, but the output stage

adder has only half the number of inputs and therefore is simpler to implement.

The folded FIR filter is illustrated in Figure 16.2.

+

Input

1

Figure 16.2 Sum

Reduced Digital Filter Circuit I

(Folded FIR)

Suppose six delay elements are used in a folded FIR filter. The multiplying coef-

ficient A4 has the same value as A2. Similarly, A5 has the same value as Al,

and A6 has the same value as AO. This symmetry can be used to reduce the

number of multiplier required: the signals from the output of delay elements 2