Page 292 - DSP Integrated Circuits

P. 292

DSP SYSTEM DESIGN

7.1 INTRODUCTION

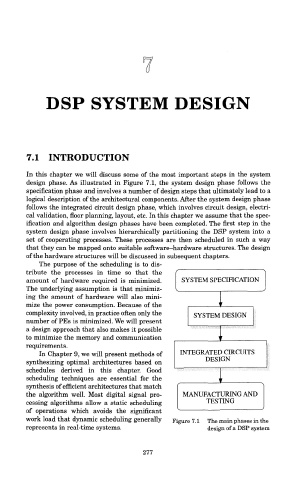

In this chapter we will discuss some of the most important steps in the system

design phase. As illustrated in Figure 7.1, the system design phase follows the

specification phase and involves a number of design steps that ultimately lead to a

logical description of the architectural components. After the system design phase

follows the integrated circuit design phase, which involves circuit design, electri-

cal validation, floor planning, layout, etc. In this chapter we assume that the spec-

ification and algorithm design phases have been completed. The first step in the

system design phase involves hierarchically partitioning the DSP system into a

set of cooperating processes. These processes are then scheduled in such a way

that they can be mapped onto suitable software-hardware structures. The design

of the hardware structures will be discussed in subsequent chapters.

The purpose of the scheduling is to dis-

tribute the processes in time so that the

amount of hardware required is minimized.

The underlying assumption is that minimiz-

ing the amount of hardware will also mini-

mize the power consumption. Because of the

complexity involved, in practice often only the

number of PEs is minimized. We will present

a design approach that also makes it possible

to minimize the memory and communication

requirements.

In Chapter 9, we will present methods of

synthesizing optimal architectures based on

schedules derived in this chapter. Good

scheduling techniques are essential for the

synthesis of efficient architectures that match

the algorithm well. Most digital signal pro-

cessing algorithms allow a static scheduling

of operations which avoids the significant

work load that dynamic scheduling generally Figure 7.1 The main phases in the

represents in real-time systems. design of a DSP system