Page 342 - DSP Integrated Circuits

P. 342

7.7 FFT Processor, Cont. 327

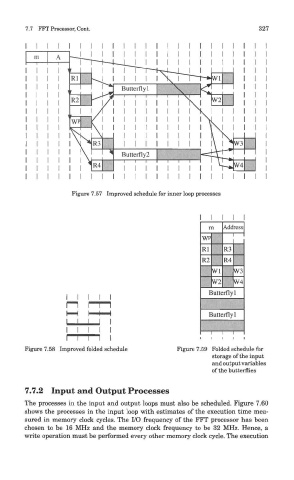

Figure 7.57 Improved schedule for inner loop processes

Figure 7.58 Improved folded schedule Figure 7.59 Folded schedule for

storage of the input

and output variables

of the butterflies

7.7.2 Input and Output Processes

The processes in the input and output loops must also be scheduled. Figure 7.60

shows the processes in the input loop with estimates of the execution time mea-

sured in memory clock cycles. The I/O frequency of the FFT processor has been

chosen to be 16 MHz and the memory clock frequency to be 32 MHz. Hence, a

write operation must be performed every other memory clock cycle. The execution