Page 416 - DSP Integrated Circuits

P. 416

9.5 Implementations Based on Complex PEs 401

system is shared by many speech channels. The system can also be used to process

the same input signal several times—for example, to implement a digital filter

bank. In applications with low work loads, one vector-multiplier can be multi-

plexed to reduce the hardware cost.

EXAMPLE 9.6

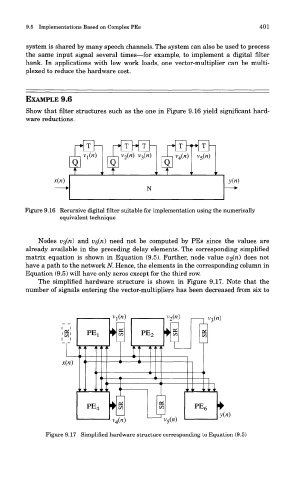

Show that filter structures such as the one in Figure 9.16 yield significant hard-

ware reductions.

Figure 9.16 Recursive digital filter suitable for implementation using the numerically

equivalent technique

Nodes 1*3(71) and v§(ri) need not be computed by PEs since the values are

already available in the preceding delay elements. The corresponding simplified

matrix equation is shown in Equation (9.5). Further, node value v^n) does not

have a path to the network N. Hence, the elements in the corresponding column in

Equation (9.5) will have only zeros except for the third row.

The simplified hardware structure is shown in Figure 9.17. Note that the

number of signals entering the vector-multipliers has been decreased from six to

Figure 9.17 Simplified hardware structure corresponding to Equation (9.5)