Page 473 - DSP Integrated Circuits

P. 473

458 Chapter 10 Digital Systems

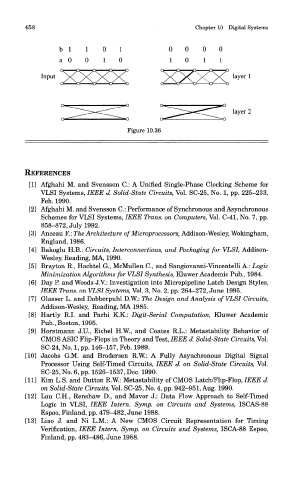

Figure 10.36

REFERENCES

[1] Afghahi M. and Svensson C.: A Unified Single-Phase Clocking Scheme for

VLSI Systems, IEEE J. Solid-State Circuits, Vol. SC-25, No. 1, pp. 225-233,

Feb. 1990.

[2] Afghahi M. and Svensson C.: Performance of Synchronous and Asynchronous

Schemes for VLSI Systems, IEEE Trans, on Computers, Vol. C-41, No. 7, pp.

858-872, July 1992.

[3] Anceau R: The Architecture of Microprocessors, Addison-Wesley, Wokingham,

England, 1986.

[4] Bakoglu H.B.: Circuits, Interconnections, and Packaging for VLSI, Addison-

Wesley, Reading, MA, 1990.

[5] Brayton R., Hachtel G., McMullen C., and Sangiovanni-Vincentelli A.: Logic

Minimization Algorithms for VLSI Synthesis, Kluwer Academic Pub., 1984.

[6] Day P. and Woods J.V.: Investigation into Micropipeline Latch Design Styles,

IEEE Trans, on VLSI Systems, Vol. 3, No. 2, pp. 264-272, June 1995.

[7] Glasser L. and Dobberpuhl D.W.: The Design and Analysis of VLSI Circuits,

Addison-Wesley, Reading, MA 1985.

[8] Hartly R.I. and Parhi K.K.: Digit-Serial Computation, Kluwer Academic

Pub., Boston, 1995.

[9] Horstmann J.U., Eichel H.W., and Coates R.L.: Metastability Behavior of

CMOS ASIC Flip-Flops in Theory and Test, IEEE J. Solid-State Circuits, Vol.

SC-24, No. 1, pp. 146-157, Feb. 1989.

[10] Jacobs G.M. and Brodersen R.W.: A Fully Asynchronous Digital Signal

Processor Using Self-Timed Circuits, IEEE J. on Solid-State Circuits, Vol.

SC-25, No. 6, pp. 1526-1537, Dec. 1990.

[11] Kim L.S. and Dutton R.W.: Metastability of CMOS Latch/Flip-Flop, IEEE J.

on Solid-State Circuits, Vol. SC-25, No. 4, pp. 942-951, Aug. 1990.

[12] Lau C.H., Renshaw D., and Mavor J.: Data Flow Approach to Self-Timed

Logic in VLSI, IEEE Intern. Symp. on Circuits and Systems, ISCAS-88

Espoo, Finland, pp. 479-482, June 1988.

[13] Liao J. and Ni L.M.: A New CMOS Circuit Representation for Timing

Verification, IEEE Intern. Symp. on Circuits and Systems, ISCA-88 Espoo,

Finland, pp. 483-486, June 1988.