Page 524 - DSP Integrated Circuits

P. 524

11.15 The Basic Shift-Accumulator 509

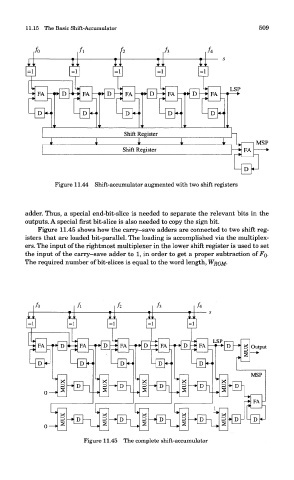

Figure 11.44 Shift-accumulator augmented with two shift registers

adder. Thus, a special end-bit-slice is needed to separate the relevant bits in the

outputs. A special first bit-slice is also needed to copy the sign bit.

Figure 11.45 shows how the carry-save adders are connected to two shift reg-

isters that are loaded bit-parallel. The loading is accomplished via the multiplex-

ers. The input of the rightmost multiplexer in the lower shift register is used to set

the input of the carry-save adder to 1, in order to get a proper subtraction of FQ.

The required number of bit-slices is equal to the word length, WRQM-

Figure 11.45 The complete shift-accumulator