Page 70 - DSP Integrated Circuits

P. 70

2.5 Trends in CMOS Technologies 55

[19] Pucknell D.A. and Eshraghian K.: Basic VLSI Design—Systems and Circuits,

Prentice Hall, NJ, 1988.

[20] Shoji M.: CMOS Digital Circuit Technology, Prentice Hall, Englewood Cliffs,

NJ1988.

[21] Sze S.M.: VLSI Technology, McGraw-Hill, New York, 1988.

[22] Tsividis Y.P.: Operation and Modeling of the MOS Transistor, McGraw-Hill,

New York, 1987.

[23] Uyemura J.P.: Fundamentals of MOS Digital Integrated Circuits, Addison-

Wesley, Reading MA, 1988.

[24] Uyemura J.P.: Circuit Design for CMOS VLSI, Kluwer Academic Pub.,

Boston, 1992.

[25] Wang N.: Digital MOS Integrated Circuits, Prentice Hall, Englewood Cliffs,

NJ, 1989.

[26] Weste N.H.E. and Eshraghian K.: Principles of CMOS VLSI Design—A

System Perspective, Addison-Wesley, Reading, MA, 1985.

[27] Wing O.: Gallium Arsenide Digital Circuits, Kluwer Academic Pub., Boston,

1990.

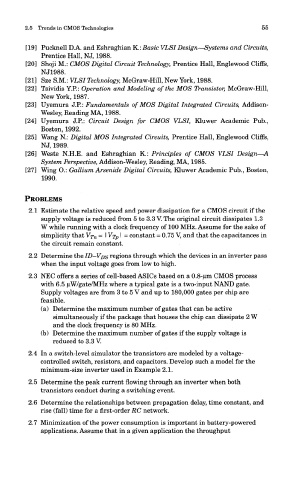

PROBLEMS

2.1 Estimate the relative speed and power dissipation for a CMOS circuit if the

supply voltage is reduced from 5 to 3.3 V. The original circuit dissipates 1.3

W while running with a clock frequency of 100 MHz. Assume for the sake of

simplicity that VT H = ' Vfp' = constant = 0.75 V, and that the capacitances in

the circuit remain constant.

2.2 Determine the ID-Vrjs regions through which the devices in an inverter pass

when the input voltage goes from low to high.

2.3 NEC offers a series of cell-based ASICs based on a 0.8-^im CMOS process

with 6.5 uW/gate/MHz where a typical gate is a two-input NAND gate.

Supply voltages are from 3 to 5 V and up to 180,000 gates per chip are

feasible.

(a) Determine the maximum number of gates that can be active

simultaneously if the package that houses the chip can dissipate 2 W

and the clock frequency is 80 MHz.

(b) Determine the maximum number of gates if the supply voltage is

reduced to 3.3 V.

2.4 In a switch-level simulator the transistors are modeled by a voltage-

controlled switch, resistors, and capacitors. Develop such a model for the

minimum-size inverter used in Example 2.1.

2.5 Determine the peak current flowing through an inverter when both

transistors conduct during a switching event.

2.6 Determine the relationships between propagation delay, time constant, and

rise (fall) time for a first-order RC network.

2.7 Minimization of the power consumption is important in battery-powered

applications. Assume that in a given application the throughput