Page 93 - Embedded Microprocessor Systems Real World Design

P. 93

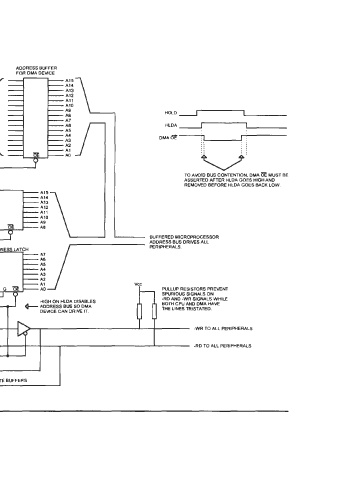

ADDRESS BUFFER

FOR DMA DEVlCE

l&WT ADDRESS

FROM DMA DEVICE

A2

AI

DMA 6€ -

TO AWID BUS CONTENTION. DMA MUST BE

Wlss CPU ASSERTED AFTER HLDA GOES HIGH AND

I REMOVED BEFORE HLDA GOES BACK LOW.

A12

All

A10

A8 - MICROPROCESSOR

MULTIPLEXED {g ADDRESS BUS DRIVES ALL

BUFFERED

PERIPHERALS

ADDRESSIDATA A3

BUS

AI

ADO PUUUP RES STORS PREVENT

SPURIOUS S GNUS ON

ALE -RD AND -WR SIGNALS WHILE

HIGH ON HLDA DISABLES BOTH CPU AND DMA *M

HLDA ADDRESS BUS SO DMA ME LINES TRiSTATED

DEVlCE CAN DRlM IT.

-WR TO ALL PERIPHERALS

-RD TO ALL PERIPHERALS

-WR FROM DMA CONTROLLER

-RD FROM DMA CONTROLLER -

Figure 2.23

Driving Address Bus During DMA.