Page 98 - Embedded Microprocessor Systems Real World Design

P. 98

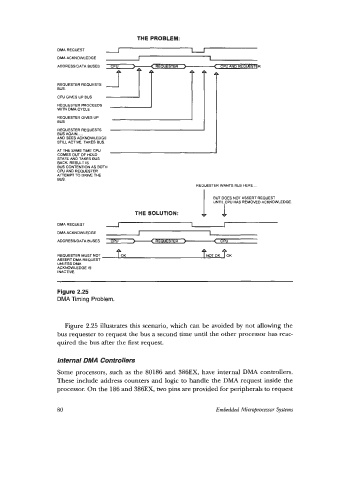

THE PROBLEM:

DMA REQUEST

DMA ACKNOWLEDGE CPU I REQUESTER I < cw AND REQUE~R

REQUESTERREQUESTS 4 ~~ 1 L

ADDRESUDATA BUSES

BUS '

WITH REQUESTERPROCEEDS J I I

CPU GIVES UP BUS

DMA

CYCLE

REQUESTER GIVES UP

BUS

REQUESTER REQUESTS I

BUS AGAIN .....

AND SEES ACKNOWLEDGE

STILL ACTIM. TAKES BUS.

AT THE SAME TIME CPU

COMES OUT OF HOLD

STATE AND TAKES BUS

BACK. RESULT IS

BUS CONTENTION AS BOTH

CPU AND REQUESTER

ATTEMPT TO DRIVE THE

BUS

REQUESTER WANTS BUS HERE ....

BUTDOESNOTASSERTREQUEST

UNTIL CPU HAS REMOVED ACKNOWLEDGE.

THE SOLUTION:

DMA REQUEST

DMA ACKNOWLEDGE

ADDRESWDATA BUSES \, CW CPU

REQUESTER MUST NOT

ASSERT DMA REQUEST

UNLESS DMA

ACKNOWLEDGE IS

INACTIM.

Figure 2.25

DMA Timing Problem.

Figure 2.25 illustrates this scenario, which can be avoided by not allowing the

bus requester to request the bus a second time until the other processor has reac-

quired the bus after the first request.

Internal DMA Controllers

Some processors, such as the 80186 and 386EX, have internal DMA controllers.

These include address counters and logic to handle the DMA request inside the

processor. On the 186 and 386EX, two pins are provided for peripherals to request

80 Embedded Microprocessor Systems