Page 71 - Hardware Implementation of Finite-Field Arithmetic

P. 71

54 Cha pte r T w o

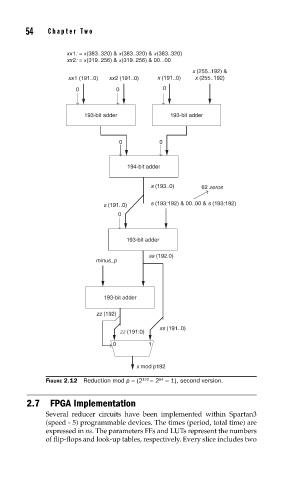

xx1: = x(383..320) & x(383..320) & x(383..320)

xx2: = x(319..256) & x(319..256) & 00...00

x (255..192) &

xx1 (191..0) xx2 (191..0) x (191..0) x (255..192)

0 0 0

193-bit adder 193-bit adder

0 0

194-bit adder

s (193..0) 62 zeros

s (191..0) s (193:192) & 00..00 & s (193:192)

0

193-bit adder

ss (192.0)

minus_p

193-bit adder

zz (192)

ss (191..0)

zz (191:0)

0 1

x mod p192

FIGURE 2.12 Reduction mod p = (2 192 − 2 64 − 1), second version.

2.7 FPGA Implementation

Several reducer circuits have been implemented within Spartan3

(speed - 5) programmable devices. The times (period, total time) are

expressed in ns. The parameters FFs and LUTs represent the numbers

of flip-flops and look-up tables, respectively. Every slice includes two