Page 72 - Hardware Implementation of Finite-Field Arithmetic

P. 72

mod m Reduction 55

flip-flops and two look-up tables. All the source files are available at

www.arithmetic-circuits.org.

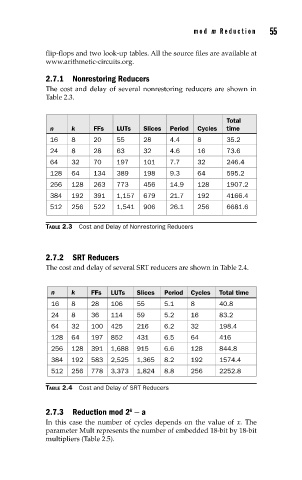

2.7.1 Nonrestoring Reducers

The cost and delay of several nonrestoring reducers are shown in

Table 2.3.

Total

n k FFs LUTs Slices Period Cycles time

16 8 20 55 28 4.4 8 35.2

24 8 28 63 32 4.6 16 73.6

64 32 70 197 101 7.7 32 246.4

128 64 134 389 198 9.3 64 595.2

256 128 263 773 456 14.9 128 1907.2

384 192 391 1,157 679 21.7 192 4166.4

512 256 522 1,541 906 26.1 256 6681.6

TABLE 2.3 Cost and Delay of Nonrestoring Reducers

2.7.2 SRT Reducers

The cost and delay of several SRT reducers are shown in Table 2.4.

n k FFs LUTs Slices Period Cycles Total time

16 8 28 106 55 5.1 8 40.8

24 8 36 114 59 5.2 16 83.2

64 32 100 425 216 6.2 32 198.4

128 64 197 852 431 6.5 64 416

256 128 391 1,688 915 6.6 128 844.8

384 192 583 2,525 1,365 8.2 192 1574.4

512 256 778 3,373 1,824 8.8 256 2252.8

TABLE 2.4 Cost and Delay of SRT Reducers

k

2.7.3 Reduction mod 2 − a

In this case the number of cycles depends on the value of x. The

parameter Mult represents the number of embedded 18-bit by 18-bit

multipliers (Table 2.5).