Page 286 - Phase-Locked Loops Design, Simulation, and Applications

P. 286

MIXED-SIGNAL PLL APPLICATIONS PART 2: FRACTIONAL-N FREQUENCY

SYNTHESIZERS Ronald E. Best 170

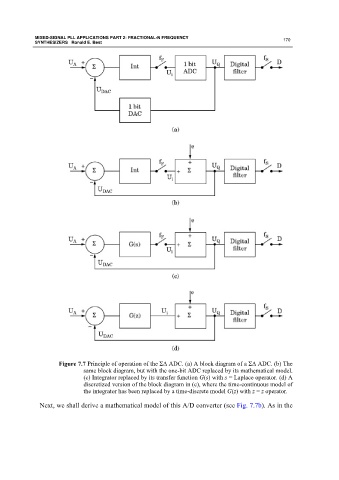

Figure 7.7 Principle of operation of the ΣΔ ADC. (a) A block diagram of a ΣΔ ADC. (b) The

same block diagram, but with the one-bit ADC replaced by its mathematical model.

(c) Integrator replaced by its transfer function G(s) with s = Laplace operator. (d) A

discretized version of the block diagram in (c), where the time-continuous model of

the integrator has been replaced by a time-discrete model G(z) with z = z operator.

Next, we shall derive a mathematical model of this A/D converter (see Fig. 7.7b). As in the