Page 1044 - The Mechatronics Handbook

P. 1044

(a) a (b)

a

c b

b f f

c a

d c

a

b

c

d d

(c) INVOLUTION GIVES (d) INVOLUTION GIVES

f(a, b, c, d) = ac + bcd + ad f(a, b, c, d) = (a + b)(a + c)(b + c + d)

DEMORGAN'S THEOREM GIVES DEMORGAN'S THEOREM GIVES

.

.

f(a, b, c, d) = ac bcd ad f(a, b, c, d) = (a + b) + (a + c) + (b + c + d)

OR IN TERMS OF THE NAND OPERATOR OR IN TERMS OF THE NOR OPERATOR

f(a, b, c, d) = (a↑c )↑(b↑c↑d )↑(a↑d ) f(a, b, c, d) = (a↓b)↓(a↓c)↓(b↓c↓d)

(e) a (f) a

c b

b f f

c a

d c

a

b

c

d d

(g) a a a = a (h) a + a = a

a a a a a

(i) a (j) a

c b

b f f

c a

d c

a b

c

d d

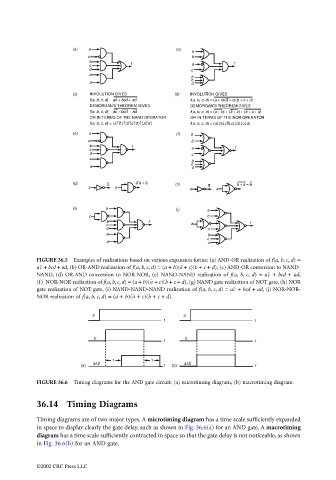

FIGURE 36.5 Examples of realizations based on various expansion forms: (a) AND-OR realization of f(a, b, c, d) =

a + bcd + ad, (b) OR-AND realization of f(a, b, c, d) = (a + b) + c)(b + c + d), (c) AND-OR conversion to NAND-

(a

c

c

NAND, (d) OR-AND conversion to NOR-NOR, (e) NAND-NAND realization of f(a, b, c, d) = a + bcd + ad,

(a

(f) NOR-NOR realization of f(a, b, c, d) = (a + b) + c)(b + c + d), (g) NAND gate realization of NOT gate, (h) NOR

c

gate realization of NOT gate, (i) NAND-NAND-NAND realization of f(a, b, c, d) = a + bcd + ad, (j) NOR-NOR-

(a

NOR realization of f(a, b, c, d) = (a + b) + c)(b + c + d).

a a

t t

b b

t t

t t

aΛb aΛb

(a) t (b) t

FIGURE 36.6 Timing diagrams for the AND gate circuit: (a) microtiming diagram, (b) macrotiming diagram.

36.14 Timing Diagrams

Timing diagrams are of two major types. A microtiming diagram has a time scale sufficiently expanded

in space to display clearly the gate delay, such as shown in Fig. 36.6(a) for an AND gate. A macrotiming

diagram has a time scale sufficiently contracted in space so that the gate delay is not noticeable, as shown

in Fig. 36.6(b) for an AND gate.

©2002 CRC Press LLC