Page 194 -

P. 194

164 CHAPTER 5 / INTERNAL MEMORY

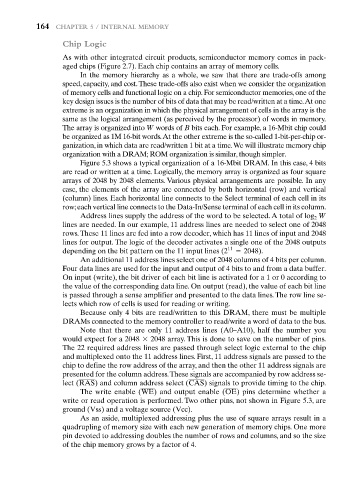

Chip Logic

As with other integrated circuit products, semiconductor memory comes in pack-

aged chips (Figure 2.7). Each chip contains an array of memory cells.

In the memory hierarchy as a whole, we saw that there are trade-offs among

speed, capacity, and cost.These trade-offs also exist when we consider the organization

of memory cells and functional logic on a chip. For semiconductor memories, one of the

key design issues is the number of bits of data that may be read/written at a time.At one

extreme is an organization in which the physical arrangement of cells in the array is the

same as the logical arrangement (as perceived by the processor) of words in memory.

The array is organized into W words of B bits each. For example, a 16-Mbit chip could

be organized as 1M 16-bit words.At the other extreme is the so-called 1-bit-per-chip or-

ganization, in which data are read/written 1 bit at a time.We will illustrate memory chip

organization with a DRAM; ROM organization is similar, though simpler.

Figure 5.3 shows a typical organization of a 16-Mbit DRAM. In this case, 4 bits

are read or written at a time. Logically, the memory array is organized as four square

arrays of 2048 by 2048 elements. Various physical arrangements are possible. In any

case, the elements of the array are connected by both horizontal (row) and vertical

(column) lines. Each horizontal line connects to the Select terminal of each cell in its

row;each vertical line connects to the Data-In/Sense terminal of each cell in its column.

W

Address lines supply the address of the word to be selected. A total of log 2

lines are needed. In our example, 11 address lines are needed to select one of 2048

rows.These 11 lines are fed into a row decoder, which has 11 lines of input and 2048

lines for output. The logic of the decoder activates a single one of the 2048 outputs

depending on the bit pattern on the 11 input lines (2 11 = 2048).

An additional 11 address lines select one of 2048 columns of 4 bits per column.

Four data lines are used for the input and output of 4 bits to and from a data buffer.

On input (write), the bit driver of each bit line is activated for a 1 or 0 according to

the value of the corresponding data line. On output (read), the value of each bit line

is passed through a sense amplifier and presented to the data lines.The row line se-

lects which row of cells is used for reading or writing.

Because only 4 bits are read/written to this DRAM, there must be multiple

DRAMs connected to the memory controller to read/write a word of data to the bus.

Note that there are only 11 address lines (A0–A10), half the number you

would expect for a 2048 * 2048 array. This is done to save on the number of pins.

The 22 required address lines are passed through select logic external to the chip

and multiplexed onto the 11 address lines. First, 11 address signals are passed to the

chip to define the row address of the array, and then the other 11 address signals are

presented for the column address.These signals are accompanied by row address se-

lect (RAS ) and column address select (CAS ) signals to provide timing to the chip.

The write enable (WE ) and output enable (OE ) pins determine whether a

write or read operation is performed. Two other pins, not shown in Figure 5.3, are

ground (Vss) and a voltage source (Vcc).

As an aside, multiplexed addressing plus the use of square arrays result in a

quadrupling of memory size with each new generation of memory chips. One more

pin devoted to addressing doubles the number of rows and columns, and so the size

of the chip memory grows by a factor of 4.