Page 364 - DSP Integrated Circuits

P. 364

References 349

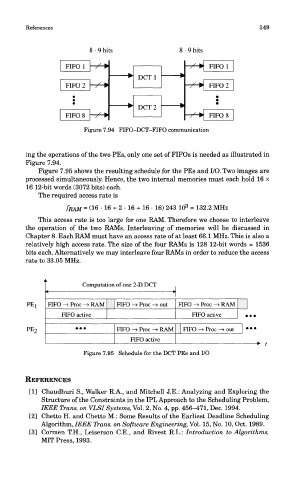

Figure 7.94 FIFO-DCT-FIFO communication

ing the operations of the two PEs, only one set of FIFOs is needed as illustrated in

Figure 7.94.

Figure 7.95 shows the resulting schedule for the PEs and I/O. Two images are

processed simultaneously. Hence, the two internal memories must each hold 16 x

16 12-bit words (3072 bits) each.

The required access rate is

This access rate is too large for one RAM. Therefore we choose to interleave

the operation of the two RAMs. Interleaving of memories will be discussed in

Chapter 8. Each RAM must have an access rate of at least 66.1 MHz. This is also a

relatively high access rate. The size of the four RAMs is 128 12-bit words = 1536

bits each. Alternatively we may interleave four RAMs in order to reduce the access

rate to 33.05 MHz.

Figure 7.95 Schedule for the DCT PEs and I/O

REFERENCES

[11 Chaudhuri S., Walker R.A., and Mitchell J.E.: Analyzing and Exploring the

Structure of the Constraints in the IPL Approach to the Scheduling Problem,

IEEE Trans, on VLSI Systems, Vol. 2, No. 4, pp. 456-471, Dec. 1994.

[2] Ghetto H. and Ghetto M.: Some Results of the Earliest Deadline Scheduling

Algorithm, IEEE Trans, on Software Engineering, Vol. 15, No. 10, Oct. 1989.

[3] Gormen T.H., Leiserson C.E., and Rivest R.L.: Introduction to Algorithms,

MIT Press, 1993.