Page 409 - DSP Integrated Circuits

P. 409

394 ChapterB Synthesis of DSP Architectures

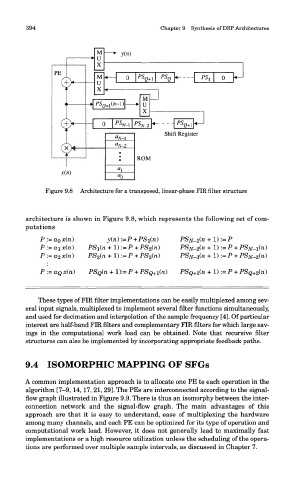

Figure 9.8 Architecture for a transposed, linear-phase FIR filter structure

architecture is shown in Figure 9.8, which represents the following set of com-

putations

These types of FIR filter implementations can be easily multiplexed among sev-

eral input signals, multiplexed to implement several filter functions simultaneously,

and used for decimation and interpolation of the sample frequency [4]. Of particular

interest are half-band FIR filters and complementary FIR filters for which large sav-

ings in the computational work load can be obtained. Note that recursive filter

structures can also be implemented by incorporating appropriate feedback paths.

9.4 ISOMORPHIC MAPPING OF SFGs

A common implementation approach is to allocate one PE to each operation in the

algorithm [7-9,14,17, 21,29]. The PEs are interconnected according to the signal-

flow graph illustrated in Figure 9.9. There is thus an isomorphy between the inter-

connection network and the signal-flow graph. The main advantages of this

approach are that it is easy to understand, ease of multiplexing the hardware

among many channels, and each PE can be optimized for its type of operation and

computational work load. However, it does not generally lead to maximally fast

implementations or a high resource utilization unless the scheduling of the opera-

tions are performed over multiple sample intervals, as discussed in Chapter 7.