Page 505 - DSP Integrated Circuits

P. 505

490 Chapter 11 Processing Elements

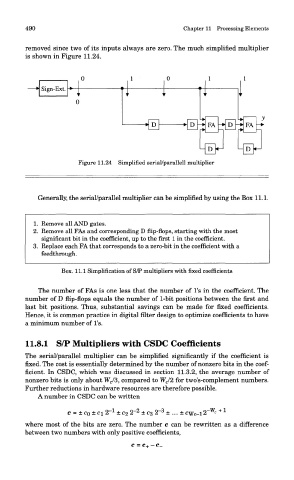

removed since two of its inputs always are zero. The much simplified multiplier

is shown in Figure 11.24.

Figure 11.24 Simplified serial/parallell multiplier

Generally, the serial/parallel multiplier can be simplified by using the Box 11.1.

1. Remove all AND gates.

2. Remove all FAs and corresponding D flip-flops, starting with the most

significant bit in the coefficient, up to the first 1 in the coefficient.

3. Replace each FA that corresponds to a zero-bit in the coefficient with a

feedthrough.

Box. 11.1 Simplification of S/P multipliers with fixed coefficients

The number of FAs is one less that the number of 1's in the coefficient. The

number of D flip-flops equals the number of 1-bit positions between the first and

last bit positions. Thus, substantial savings can be made for fixed coefficients.

Hence, it is common practice in digital filter design to optimize coefficients to have

a minimum number of 1's.

11.8.1 S/P Multipliers with CSDC Coefficients

The serial/parallel multiplier can be simplified significantly if the coefficient is

fixed. The cost is essentially determined by the number of nonzero bits in the coef-

ficient. In CSDC, which was discussed in section 11.3.2, the average number of

nonzero bits is only about W c/3, compared to W c/2 for two's-complement numbers.

Further reductions in hardware resources are therefore possible.

A number in CSDC can be written

where most of the bits are zero. The number c can be rewritten as a difference

between two numbers with only positive coefficients,