Page 506 - DSP Integrated Circuits

P. 506

11.9 Minimum Number of Basic Operations 491

A multiplication can now be written

where represents the original value with all bits inverted. Obviously, the multipli-

cation can be implemented using the technique just discussed, except the ^-inputs

to the FAs in bit positions with negative coefficient weights are inverted, and the

corresponding carry D flip-flops are initially set.

EXAMPLE 11.8

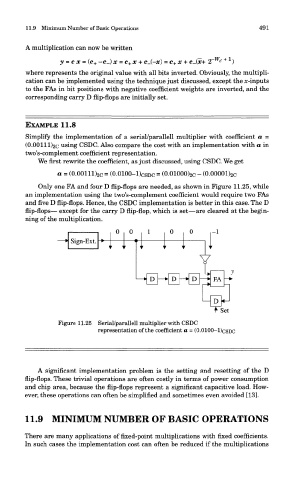

Simplify the implementation of a serial/parallell multiplier with coefficient a =

(0.00111)2c using CSDC. Also compare the cost with an implementation with a in

two's-complement coefficient representation.

We first rewrite the coefficient, as just discussed, using CSDC. We get

Only one FA and four D flip-flops are needed, as shown in Figure 11.25, while

an implementation using the two's-complement coefficient would require two FAs

and five D flip-flops. Hence, the CSDC implementation is better in this case. The D

flip-flops— except for the carry D flip-flop, which is set—are cleared at the begin-

ning of the multiplication.

Figure 11.25 Serial/parallell multiplier with CSDC

representation of the coefficient a = (0.0100—l)csDC

A significant implementation problem is the setting and resetting of the D

flip-flops. These trivial operations are often costly in terms of power consumption

and chip area, because the flip-flops represent a significant capacitive load. How-

ever, these operations can often be simplified and sometimes even avoided [13].

11.9 MINIMUM NUMBER OF BASIC OPERATIONS

There are many applications of fixed-point multiplications with fixed coefficients.

In such cases the implementation cost can often be reduced if the multiplications