Page 502 - DSP Integrated Circuits

P. 502

11.7 Bit-Serial Two-Port Adaptor 487

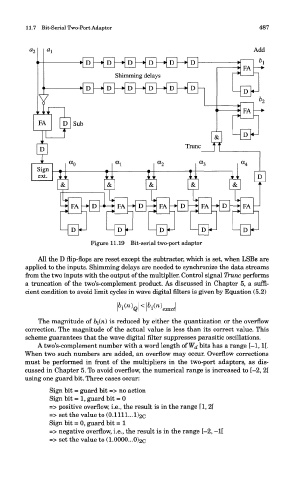

Figure 11.19 Bit-serial two-port adaptor

All the D flip-flops are reset except the subtracter, which is set, when LSBs are

applied to the inputs. Shimming delays are needed to synchronize the data streams

from the two inputs with the output of the multiplier. Control signal Trunc performs

a truncation of the two's-complement product. As discussed in Chapter 5, a suffi-

cient condition to avoid limit cycles in wave digital filters is given by Equation (5.2)

The magnitude of b{(n) is reduced by either the quantization or the overflow

correction. The magnitude of the actual value is less than its correct value. This

scheme guarantees that the wave digital filter suppresses parasitic oscillations.

A two's-complement number with a word length of W^ bits has a range [-1,1[.

When two such numbers are added, an overflow may occur. Overflow corrections

must be performed in front of the multipliers in the two-port adaptors, as dis-

cussed in Chapter 5. To avoid overflow, the numerical range is increased to [-2, 2[

using one guard bit. Three cases occur:

Sign bit = guard bit => no action

Sign bit = 1, guard bit = 0

=> positive overflow, i.e., the result is in the range [1, 2[

=> set the value to (0.1111...1)2C

Sign bit = 0, guard bit = 1

=> negative overflow, i.e., the result is in the range [-2, -1[

=> set the value to (1.0000...0) 2c