Page 543 - DSP Integrated Circuits

P. 543

528 Chapter 11 Processing Elements

(a) Express the word length in the WRQM in terms of the coefficients a;.

an

(b) How is the hardware cost and throughput related to WRQM d W^?

11.16 A fourth-order digital filter is realized in cascade form using second-order

sections in direct form II. The second-order sections are implemented using

distributed arithmetic. How many PEs are required? How many words are

required in the ROMs? Sketch the major parts of the implementation.

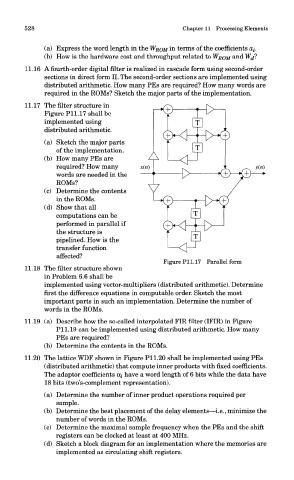

11.17 The filter structure in

Figure PI 1.17 shall be

implemented using

distributed arithmetic.

(a) Sketch the major parts

of the implementation.

(b) How many PEs are

required? How many

words are needed in the

ROMs?

(c) Determine the contents

in the ROMs.

(d) Show that all

computations can be

performed in parallel if

the structure is

pipelined. How is the

transfer function

affected?

Figure PI 1.17 Parallel form

11.18 The filter structure shown

in Problem 6.6 shall be

implemented using vector-multipliers (distributed arithmetic). Determine

first the difference equations in computable order. Sketch the most

important parts in such an implementation. Determine the number of

words in the ROMs.

11.19 (a) Describe how the so-called interpolated FIR filter (IFIR) in Figure

PI 1.19 can be implemented using distributed arithmetic. How many

PEs are required?

(b) Determine the contents in the ROMs.

11.20 The lattice WDF shown in Figure P11.20 shall be implemented using PEs

(distributed arithmetic) that compute inner products with fixed coefficients.

The adaptor coefficients a; have a word length of 6 bits while the data have

18 bits (two's-complement representation).

(a) Determine the number of inner product operations required per

sample.

(b) Determine the best placement of the delay elements—i.e., minimize the

number of words in the ROMs.

(c) Determine the maximal sample frequency when the PEs and the shift

registers can be clocked at least at 400 MHz.

(d) Sketch a block diagram for an implementation where the memories are

implemented as circulating shift registers.