Page 540 - DSP Integrated Circuits

P. 540

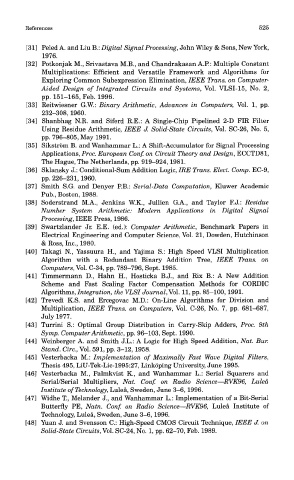

References 525

[31] Peled A. and Liu B.: Digital Signal Processing, John Wiley & Sons, New York,

1976.

[32] Potkonjak M., Srivastava M.B., and Chandrakasan A.P.: Multiple Constant

Multiplications: Efficient and Versatile Framework and Algorithms for

Exploring Common Subexpression Elimination, IEEE Trans, on Computer-

Aided Design of Integrated Circuits and Systems, Vol. VLSI-15, No. 2,

pp. 151-165, Feb. 1996.

[33] Reitwiesner G.W.: Binary Arithmetic, Advances in Computers, Vol. 1, pp.

232-308,1960.

[34] Shanbhag N.R. and Siferd R.E.: A Single-Chip Pipelined 2-D FIR Filter

Using Residue Arithmetic, IEEE J. Solid-State Circuits, Vol. SC-26, No. 5,

pp. 796-805, May 1991.

[35] Sikstrom B. and Wanhammar L.: A Shift-Accumulator for Signal Processing

Applications, Proc. European Conf. on Circuit Theory and Design, ECCTD81,

The Hague, The Netherlands, pp. 919-924,1981.

[36] Sklansky J.: Conditional-Sum Addition Logic, IRE Trans. Elect. Comp. EC-9,

pp. 226-231, 1960.

[37] Smith S.G. and Denyer P.B.: Serial-Data Computation, Kluwer Academic

Pub., Boston, 1988.

[38] Soderstrand M.A., Jenkins W.K., Jullien G.A., and Taylor F.J.: Residue

Number System Arithmetic: Modern Applications in Digital Signal

Processing, IEEE Press, 1986.

[39] Swartzlander Jr. E.E. (ed.): Computer Arithmetic, Benchmark Papers in

Electrical Engineering and Computer Science, Vol. 21, Dowden, Hutchinson

& Ross, Inc., 1980.

[40] Takagi N., Yassuura H., and Yajima S.: High Speed VLSI Multiplication

Algorithm with a Redundant Binary Addition Tree, IEEE Trans, on

Computers, Vol. C-34, pp. 789-796, Sept. 1985.

[41] Timmermann D., Hahn H., Hosticka B.J., and Rix B.: A New Addition

Scheme and Fast Scaling Factor Compensation Methods for CORDIC

Algorithms, Integration, the VLSIJournal,Vo\. 11, pp. 85-100,1991.

[42] Trevedi K.S. and Ercegovac M.D.: On-Line Algorithms for Division and

Multiplication, IEEE Trans, on Computers, Vol. C-26, No. 7, pp. 681-687,

July 1977.

[43] Turrini S.: Optimal Group Distribution in Carry-Skip Adders, Proc. 9th

Symp. Computer Arithmetic, pp. 96-103, Sept. 1990.

[44] Weinberger A. and Smith J.L.: A Logic for High Speed Addition, Nat. Bur.

Stand. Circ., Vol. 591, pp. 3-12,1958.

[45] Vesterbacka M.: Implementation of Maximally Fast Wave Digital Filters,

Thesis 495, LiU-Tek-Lic-1995:27, Linkoping University, June 1995.

[46] Vesterbacka M., Palmkvist K., and Wanhammar L.: Serial Squarers and

Serial/Serial Multipliers, Nat. Conf. on Radio Science—RVK96, Lulea

Institute of Technology, Lulea, Sweden, June 3-6, 1996.

[47] Widhe T, Melander J., and Wanhammar L.: Implementation of a Bit-Serial

Butterfly PE, Natn. Conf. on Radio Science—RVK96, Lulea Institute of

Technology, Lulea, Sweden, June 3-6,1996.

[48] Yuan J. and Svensson C.: High-Speed CMOS Circuit Technique, IEEE J. on

Solid-State Circuits,Vol. SC-24, No. 1, pp. 62-70, Feb. 1989.