Page 718 - Engineering Digital Design

P. 718

684 CHAPTER 14/ASYNCHRONOUS STATE MACHINE DESIGN AND ANALYSIS

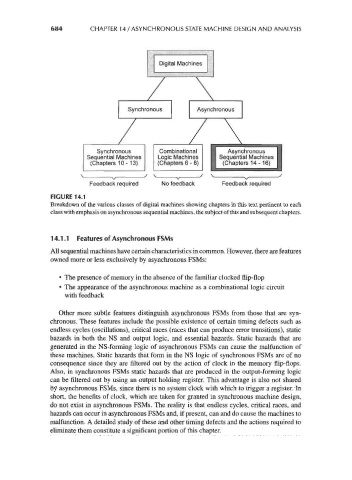

Digital Machines

Synchronous Asynchronous

Sequential Machines Sequential Machines

(Chapters 10-13) (Chapters 14-16)

Feedback required No feedback Feedback required

FIGURE 14.1

Breakdown of the various classes of digital machines showing chapters in this text pertinent to each

class with emphasis on asynchronous sequential machines, the subject of this and subsequent chapters.

14.1.1 Features of Asynchronous FSMs

All sequential machines have certain characteristics in common. However, there are features

owned more or less exclusively by asynchronous FSMs:

• The presence of memory in the absence of the familiar clocked flip-flop

• The appearance of the asynchronous machine as a combinational logic circuit

with feedback

Other more subtle features distinguish asynchronous FSMs from those that are syn-

chronous. These features include the possible existence of certain timing defects such as

endless cycles (oscillations), critical races (races that can produce error transitions), static

hazards in both the NS and output logic, and essential hazards. Static hazards that are

generated in the NS-forming logic of asynchronous FSMs can cause the malfunction of

these machines. Static hazards that form in the NS logic of synchronous FSMs are of no

consequence since they are filtered out by the action of clock in the memory flip-flops.

Also, in synchronous FSMs static hazards that are produced in the output-forming logic

can be filtered out by using an output holding register. This advantage is also not shared

by asynchronous FSMs, since there is no system clock with which to trigger a register. In

short, the benefits of clock, which are taken for granted in synchronous machine design,

do not exist in asynchronous FSMs. The reality is that endless cycles, critical races, and

hazards can occur in asynchronous FSMs and, if present, can and do cause the machines to

malfunction. A detailed study of these and other timing defects and the actions required to

eliminate them constitute a significant portion of this chapter.