Page 383 - DSP Integrated Circuits

P. 383

368 Chapter 8 DSP Architectures

Many DSP algorithms have an inherent hierarchy that can be mirrored

directly by the control structure. For example, the nested loops in the FFT have

such a hierarchical structure. It is often efficient to map a hierarchy of signals to a

hierarchical control structure.

8.4.5 Synchronous and Asynchronous Systems

There was no "One, two, three, and away," but they began running

when they liked and left off when they liked, so that it was not easy to

know when the race was over.

Lewis Carroll

Timing philosophy; is one of the most important attributes characterizing a com-

puting system. There are two types of possible timing schemes—synchronous and

asynchronous.

Synchronous timing techniques, which are the most commonly used tech-

niques, are characterized by the existence of a global clock that defines the basic

unit of time. This time reference is used to order the activities into a proper

sequence. The whole system is an isosynchronous domain. This is in practice

accomplished by a central, global clock that broadcasts clock signals to all units in

the system so that the entire system operates in a lock-step fashion.

Asynchronous timing techniques operate without a global clock. Communica-

tion among operational units is performed by means of interlock handshaking

schemes. Asynchronous systems are difficult to design, and communication between

synchronous and asynchronous systems is difficult and may cause malfunction.

8.4.6 Self-Timed Systems

A man with a watch knows the time.

A man with two watches is not sure.

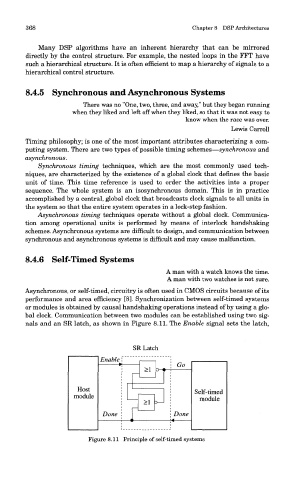

Asynchronous, or self-timed, circuitry is often used in CMOS circuits because of its

performance and area efficiency [8]. Synchronization between self-timed systems

or modules is obtained by causal handshaking operations instead of by using a glo-

bal clock. Communication between two modules can be established using two sig-

nals and an SR latch, as shown in Figure 8.11. The Enable signal sets the latch,

Figure 8.11 Principle of self-timed systems