Page 385 - DSP Integrated Circuits

P. 385

370 Chapters DSP Architectures

Timing and synchronization problems are alleviated in this approach due to

the inherent decomposition of the system into independent isochronous parts. The

clock skew problem is changed into a communication problem between isochro-

nous zones. We will use this technique of handshaking in the three case studies to

interface the fast bit-serial processing elements with the main memories.

8.5 MULTIPROCESSORS AND MULTICOMPUTERS

General-purpose parallel or distributed computer systems can be divided into two

categories: multiprocessors and multicomputers [9]. The main difference between

these two categories lies in the way in which communication between the proces-

sors is organized.

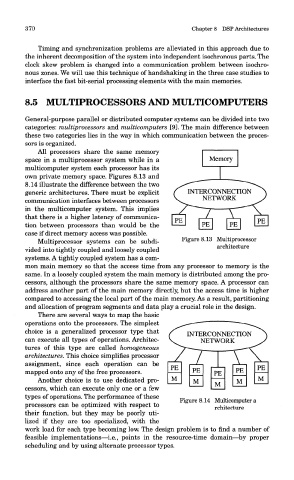

All processors share the same memory

space in a multiprocessor system while in a

multicomputer system each processor has its

own private memory space. Figures 8.13 and

8.14 illustrate the difference between the two

generic architectures. There must be explicit

communication interfaces between processors

in the multicomputer system. This implies

that there is a higher latency of communica-

tion between processors than would be the

case if direct memory access was possible.

Figure 8.13 Multiprocessor

Multiprocessor systems can be subdi-

architecture

vided into tightly coupled and loosely coupled

systems. A tightly coupled system has a com-

mon main memory so mat tne access time irom any processor to memory is tne

same. In a loosely coupled system the main memory is distributed among the pro-

cessors, although the processors share the same memory space. A processor can

address another part of the main memory directly, but the access time is higher

compared to accessing the local part of the main memory. As a result, partitioning

and allocation of program segments and data play a crucial role in the design.

mere are several ways to map me oasic

operations onto the processors. The simplest

choice is a generalized processor type that

can execute all types of operations. Architec-

tures of this type are called homogeneous

architectures. This choice simplifies processor

assignment, since each operation can be

mapped onto any of the free processors.

Another choice is to use dedicated pro-

cessors, which can execute only one or a few

types of operations. The performance of these

Figure 8.14 Multicomputer a

processors can be optimized with respect to rchitecture

their function, but they may be poorly uti-

lized if they are too specialized, with the

work load for each type becoming low. The design problem is to find a number of

feasible implementations—i.e., points in the resource-time domain—by proper

scheduling and by using alternate processor types.